Первые микроконтроллеры с ядром AVR (аббревиатура производная от имен двух главных разработчиков Alf-Egil Bogen + Vegard Wollen + RISC) увидели свет в 1997г и начали стремительно завоевывать нишу на рынке 8-разрядных микроконтроллеров для встраиваемых систем. А уже через несколько лет своего становления AVR превратились в основное направление развития компании Atmel.

Первопроходцем стало семейство Classic, которое сейчас уже полностью снято с производства. Первые модели Classic были немного “сыроватыми” (что, впрочем, характерно и для многих других сложных изделий) и вызывали различные нарекания по поводу стабильности работы, надежности энергонезависимой памяти и т.д. Однако со временем недостатки были устранены, а основные концепции Atmel увидели свое продолжение в двух семействах нового поколения ATtiny (младшее семейство) и ATmega (старшее семейство). В данный момент микроконтроллеры ATtiny и ATmega составляют основную массу изделий AVR (характеристики микроконтроллеров ATtiny и ATmega приведены в приложении A). Но сказать, что на этом их развитие завершилось, конечно, нельзя. На сегодняшний день ядро AVR лежит в основе целого ряда микроконтроллеров для специализированных приложений. К ним относятся модели, содержащие на своем борту CAN (AT90CAN), USB (AT90USB), модули для генерации ШИМ (AT90PWM), радиочастотный модуль (AT86RF), а также конфигурируемые микроконтроллеры, которые совмещают на одном кристалле процессор и программируемые массивы FPGA.

Со второй половины 2008 г начался серийный выпуск моделей микроконтроллеров семейства Xmega. Архитектура AVR перетерпела значительную переработку. Были устранены многие слабые места. В составе Xmega появились контроллеры прерываний и прямого доступа к памяти, 12-разрядные АЦП и ЦАП, дополнительные модули таймеров-счетчиков и мн. др. Память EEPROM стала проецироваться на адресное пространство SRAM. Напряжение питания снизилось до 3.3 В, а максимальная тактовая частота процессора Xmega возросла до 32 МГц.

Каждый год объем продаж AVR-микроконтроллеров увеличивается примерно в два раза, а общее их выпущенное количество уже давно перевалило за полмиллиарда. В электронной промышленности AVR стали безоговорочным индустриальным стандартом.

Особенности архитектуры

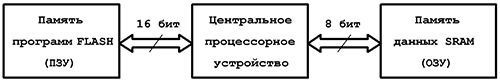

Как и подавляющее большинство современных 8-разрядных микроконтроллеров, AVR является типичным представителем архитектуры Гарвардского типа. Память программ и память данных в нем отделены друг от друга и находятся в различных адресных пространствах (см. рис.1). ЦПУ имеет две независимые шины: 16-разрядную для обращения к ПЗУ и 8-разрядную для взаимодействия с ОЗУ. Длина слова команды у AVR кратна 16-ти битам и может составлять 2 или 4 байта.

Рис.1 Разделение памяти программ и данных в Гарвардской архитектуре

Гарвардская архитектура дает возможность одновременно осуществлять выборку команд из ПЗУ и производить операции над переменными в ОЗУ, что дает существенный прирост производительности. В этом случае, однако, микроконтроллер может выполнять команды только из ПЗУ, но для большинства приложений, где предполагается его использование, это не имеет серьезного значения.

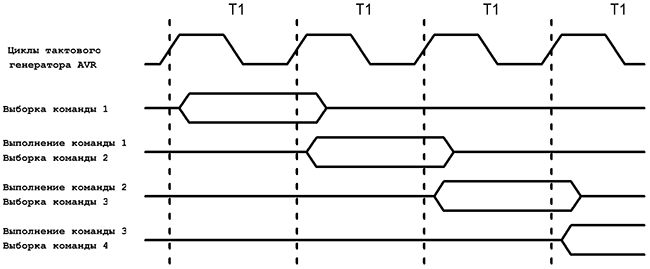

Рис.2 Работа конвейера команд

В микроконтроллерах AVR реализован двухступенчатый конвейер команд (см. рис.2). Во время выполнения текущей команды, происходит выборка и декодирование следующей инструкции. Функционирование конвейера нарушается только в те моменты, когда результат выполнения команды не определен. Это относится к командам типа Test & Skip (Проверка и пропуск) и аппаратным прерываниям. В первом случае происходит ветвление по условию, которое заранее неизвестно, а во втором – программный переход в неопределенный момент времени.

AVR имеют систему команд RISC (Reduced Instruct Set Computers – компьютеры с сокращённым набором команд). Такая система подразумевает наличие небольшого, хорошо продуманного набора команд, большая часть из которых выполняется за одинаковый промежуток времени (машинный цикл). Машинный цикл ядра AVR – 1 период тактовой частоты системного генератора. Это означает, что производительность микроконтроллера составляет 1 MIPS (Millions Instruction Per Second) на 1 МГц (!) или 20 MIPS при наибольшей частоте 20 МГц.

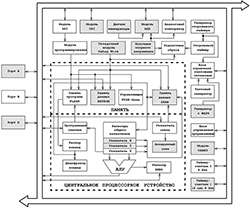

Рис.3 Внутреннее устройство микроконтроллеров семейства ATtiny

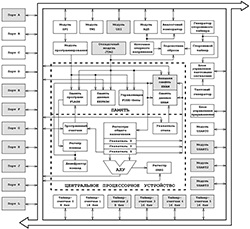

Внутренняя структура микроконтроллеров семейства ATtiny приведена на рис.3, а семейства ATmega на рис.4. Аппаратные модули, закрашенные серым цветом, имеются не во всех моделях AVR.

Рис.4 Внутреннее устройство микроконтроллеров семейства ATmega

Перейти к следующей части: Память - Память программ FLASH

Котов Игорь Юрьевич

Котов Игорь Юрьевич

Опубликована: 2012 г.

Опубликована: 2012 г.

Вознаградить

Вознаградить

Комментарии (1) |

Я собрал (0) |

Подписаться

|

Я собрал (0) |

Подписаться

Для добавления Вашей сборки необходима регистрация