Интерес к теме ПЛИС растет постоянно, но порог вхождения высокий. Даже покупка дорогой отладочной платы мало спасает ситуацию, т.к. для изучения 80% материалов не требуется отладочная плата. Процесс создания модулей для тестирования представляет серьезную проблему для новичков и требует много времени и сил для преодоления порога вхождения. Кроме того, знакомство с моделированием позволит на практике ознакомится с созданием и работой цифровых устройств на практике без дополнительных расходов.

Цель статьи заполнить данный пробел и по шагам показать процесс создания связки Целевой модуль =>Тестбенч. Проекты делаю на языке VHDL в САПР Vivado от Xilinx.

1. Создание проекта

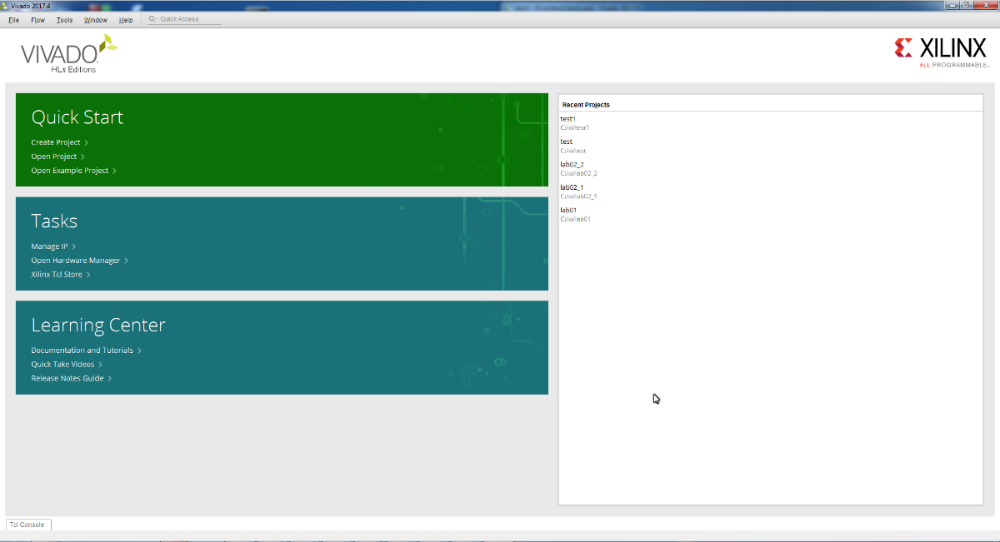

Стартовая страницы Vivado. Создаем наш будущий проект. В имени проекта не должно быть русских букв и полный адрес должен быть не более 255 символов.

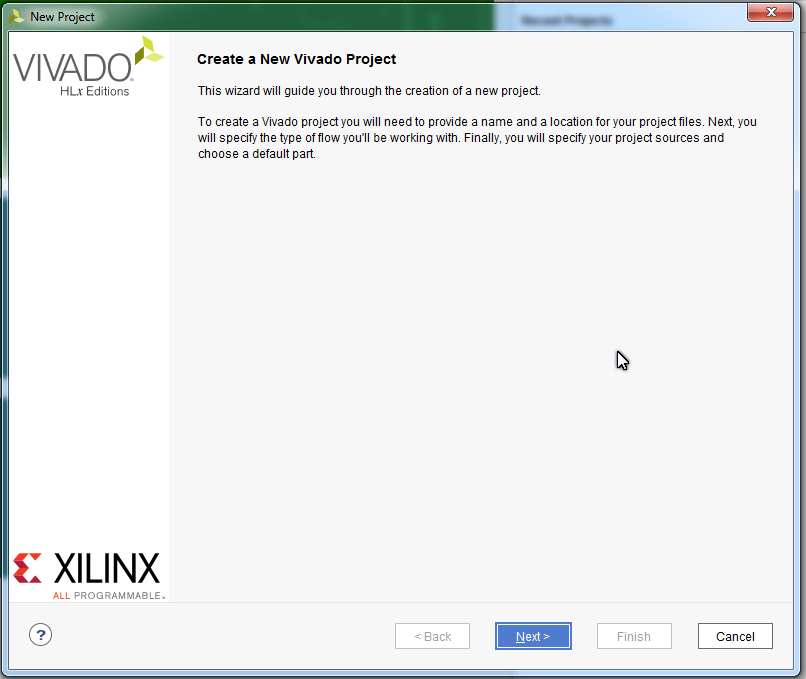

Создаем проект

Указываем место расположения проекта

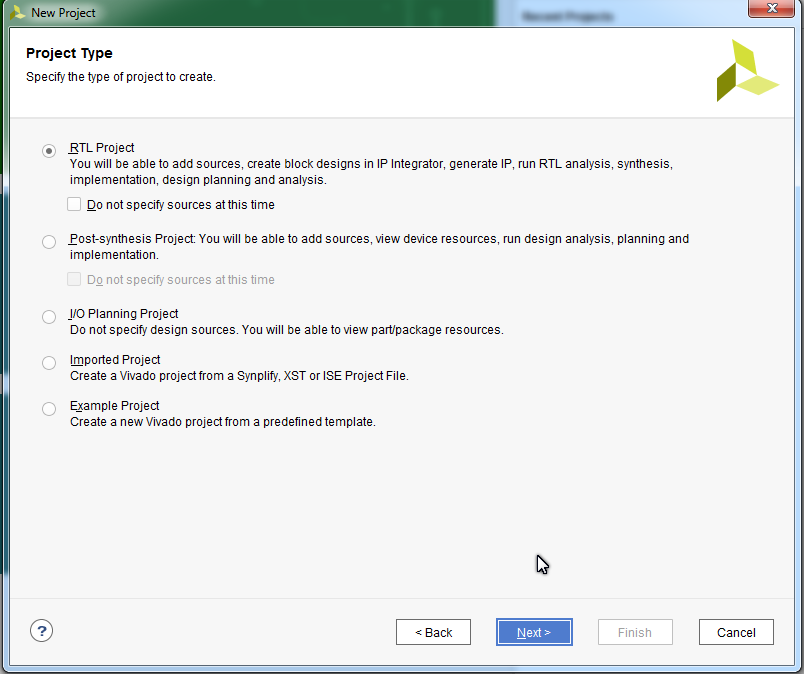

Выбираем RTL проект

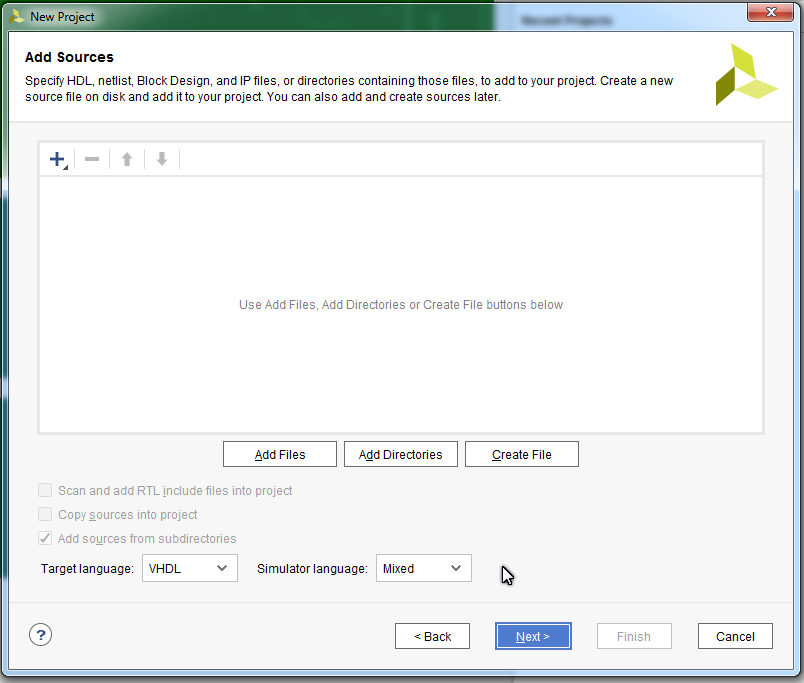

Ничего не добавляем в проект

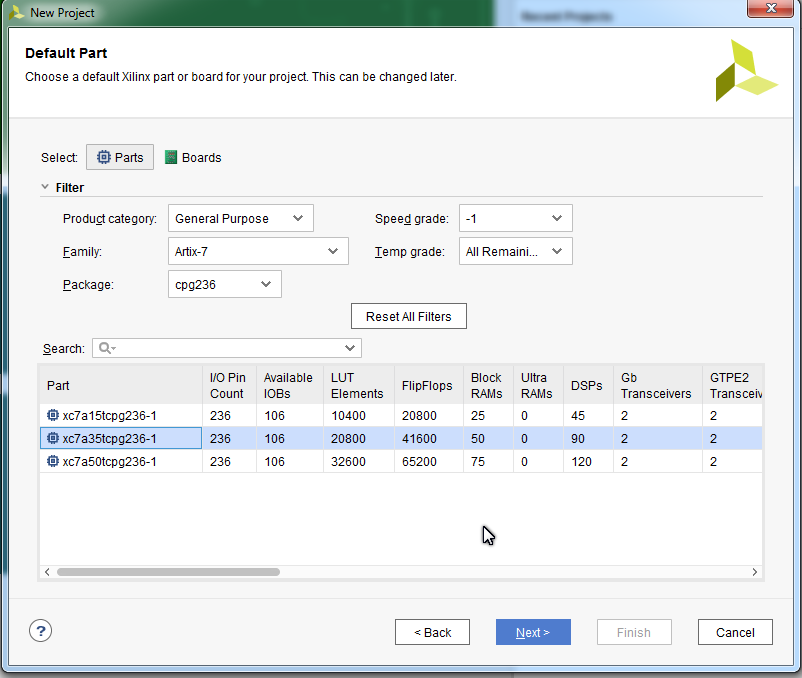

Выбираем нашу целевую ПЛИС. В данном случае я выбрал ПЛИС которая стоит на отладочной плате Digilent Basys 3.

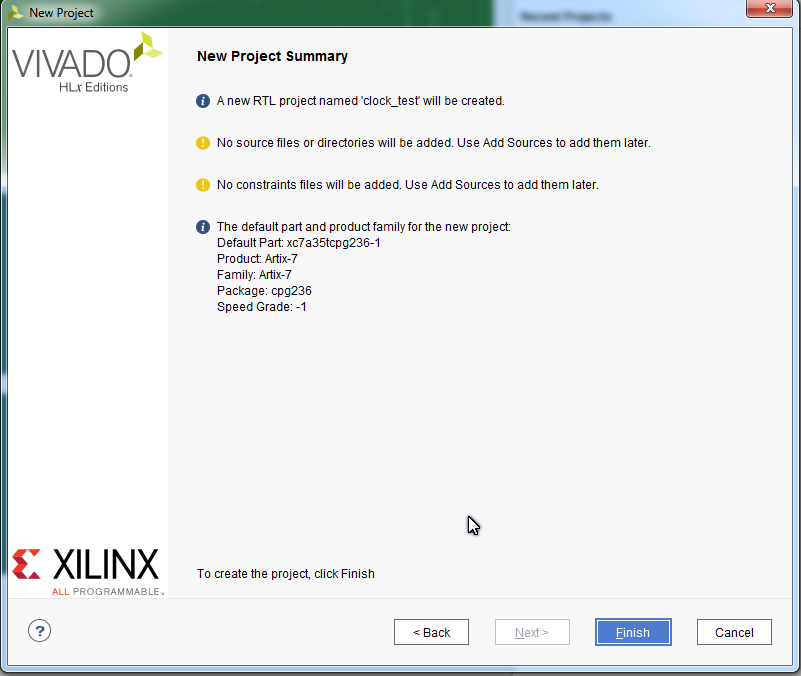

Подтверждаем создание проекта.

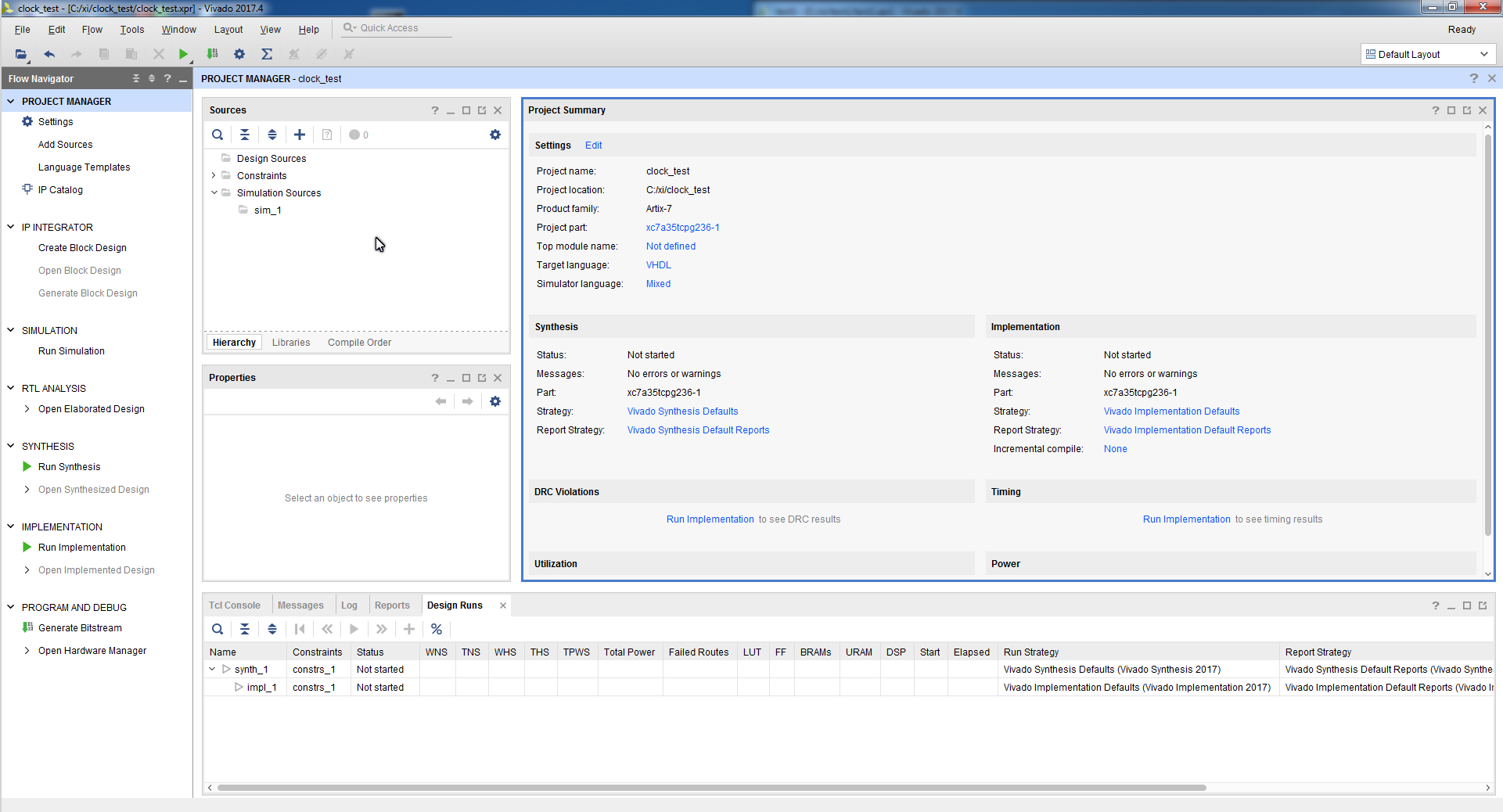

Созданный проект

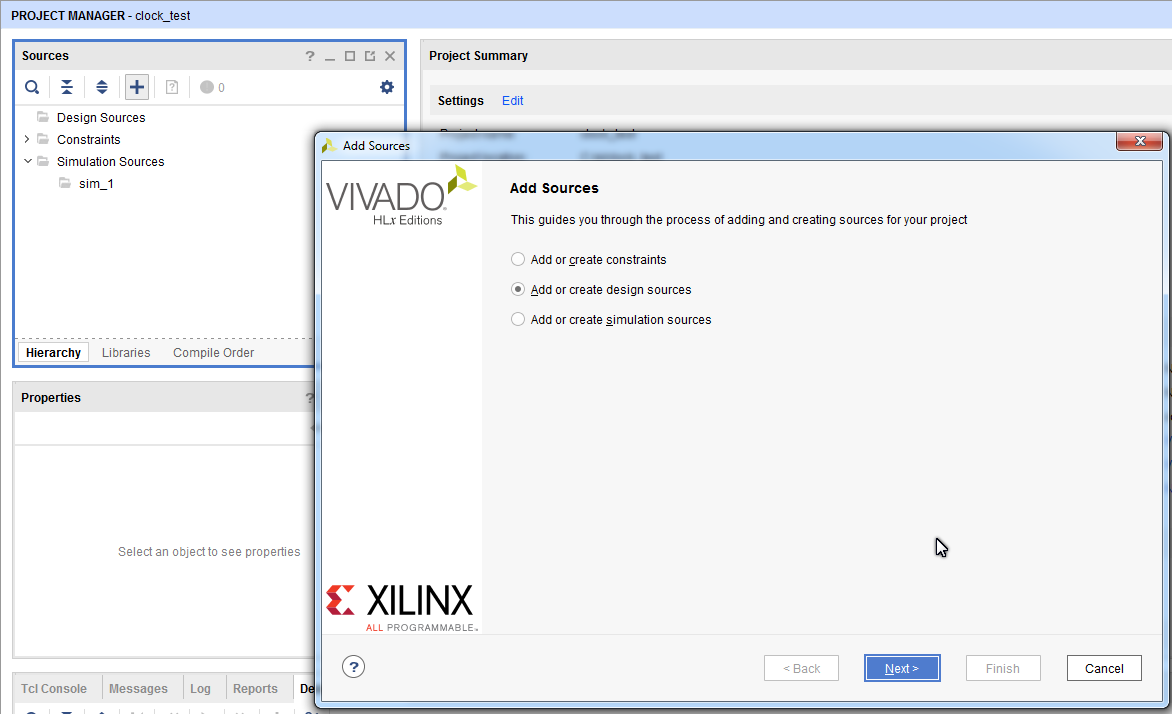

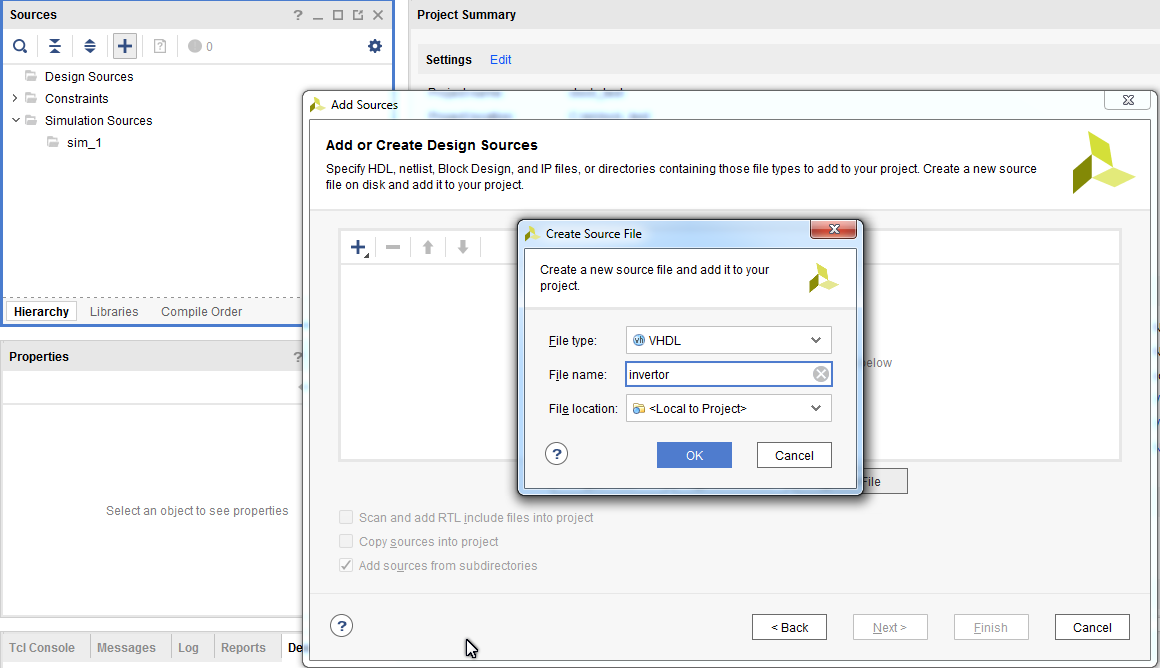

Добавляем в проект основной модуль, который затем планируется загрузить в FPGA. Для этого нажимаем на значок "+" в окне Sources

Вводим название нашего модуля

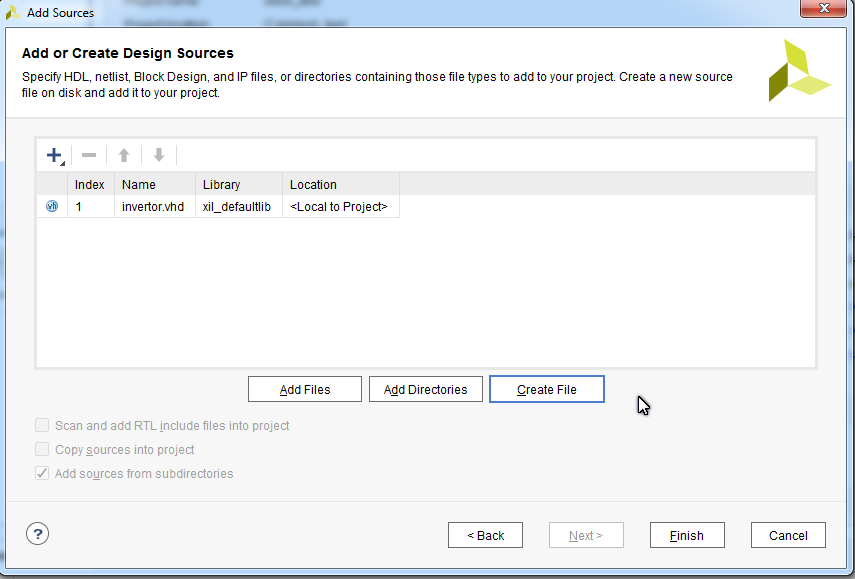

Подтверждаем добавление основного модуля.

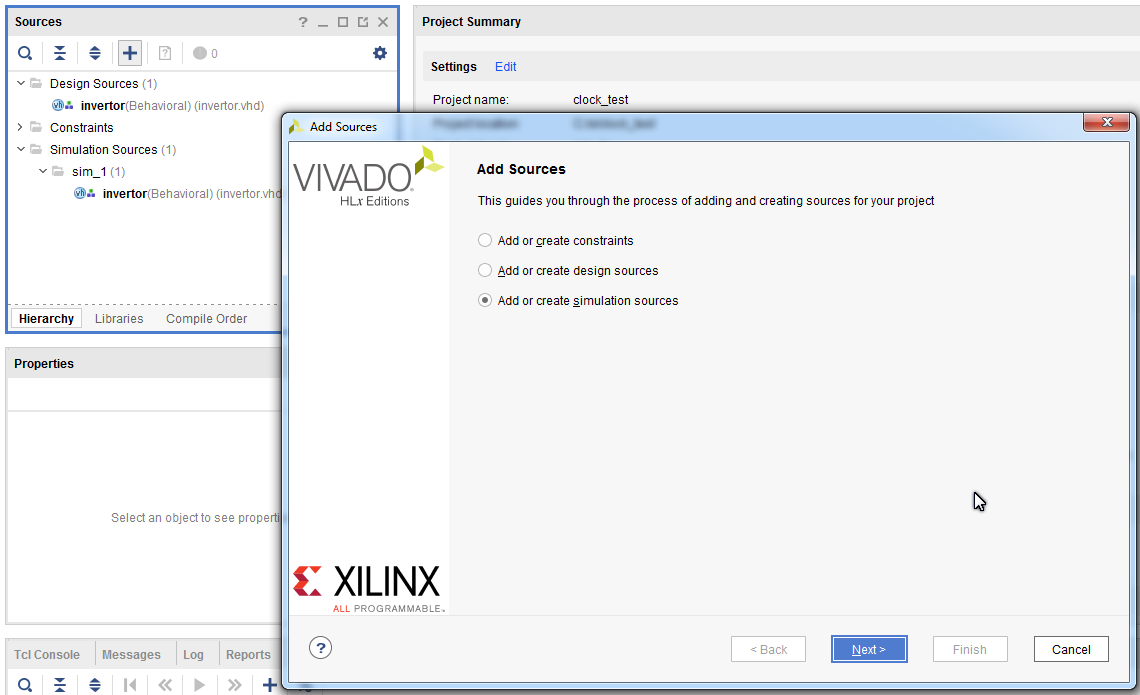

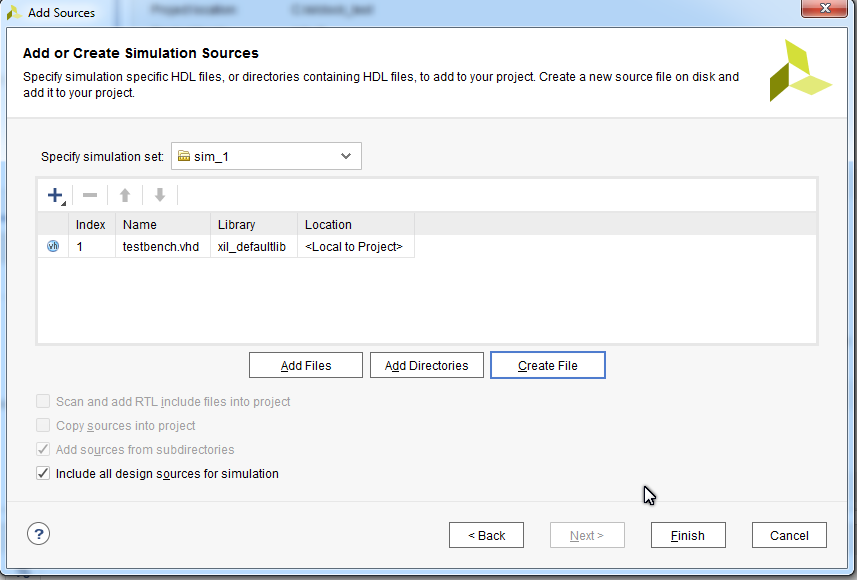

Добавляем модуль для testbench.

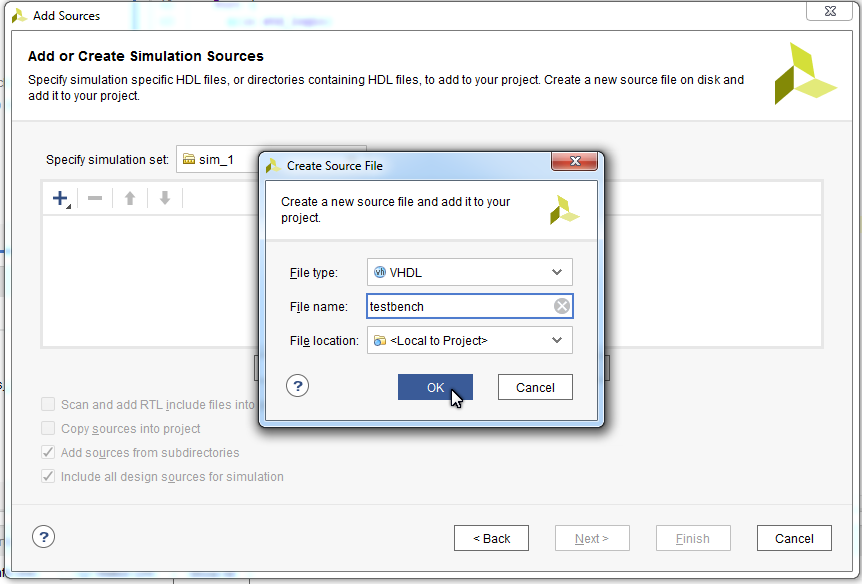

Вводим название для testbench

Подтверждаем добавления нашего testbench

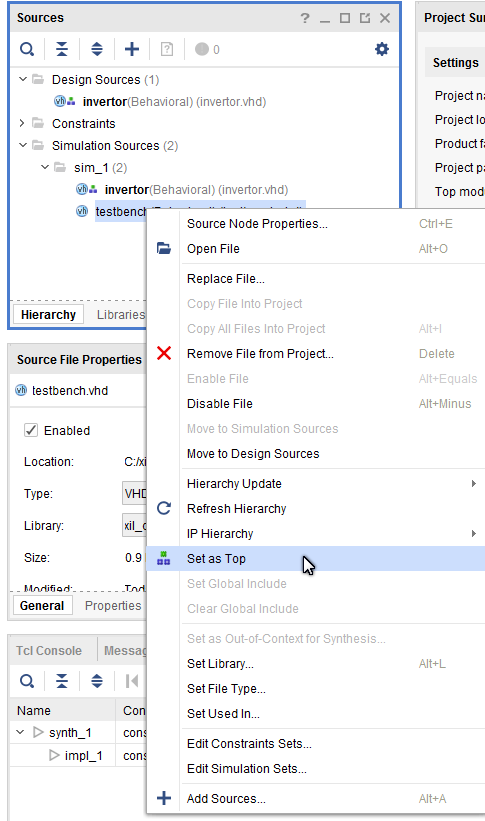

Для того, чтобы testbench запустился при симуляции необходимо его сделать Top.

Для этого на кликаем по правой кнопке мыши, и выбираем в меню Set as Top

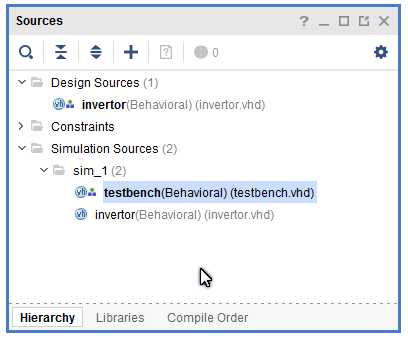

В результате получим такое окно

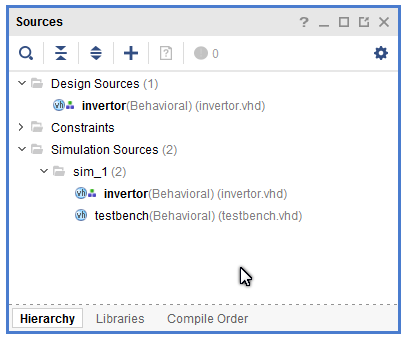

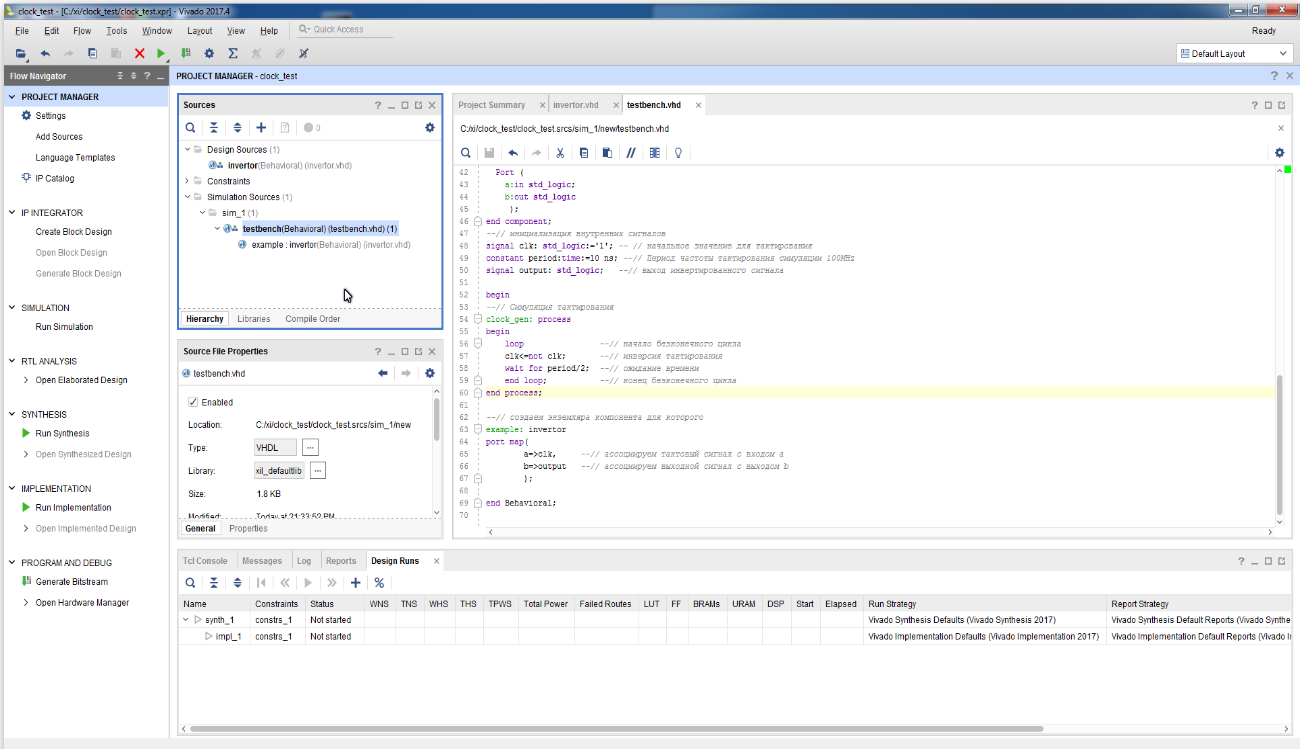

После вставки кода в файлы invertor и testbench получим следующую вид проекта

2. Написание основного модуля и тестбенча для него

При работе с ПЛИС можно разделить проект на целевые модули и модули для тестирования еще их называют testbench. Без testbench невозможно изучать языки HDL и стандартные конструкции проектирования схем. Приведу шаблон для симуляции генерации тактирования и подключения модуля invertor.

Напишем простой модуль для основного модуля invertor который инвертирует входящий сигнал на языке VHDL. Комментарии начинаются после двух тире "- -". Каждый модуль находится в своем файле.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following library declaration if instantiating

-- any Xilinx leaf cells in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

--// описание целевого модуля

entity invertor is

Port (

a:in std_logic; --// входящий сигнал

b:out std_logic -- // исходящий сигнал

);

end invertor;

--// реализация модуля

architecture Behavioral of invertor is

begin

b<= not a; -- // инверсия входящего сигнала

end Behavioral;

Entity - это такой черный ящик, который имеет входы и выходы, а Architecture - это реализация логики этого черного ящика. Благодаря условному синтезу, у одного ящика может быть множество реализаций. Когда мы обозначаем Top значит мы выбрали основной черный ящик в который мы будем класть другие черные ящик и соединять их сигналами.

Ниже приведен текст testbench для модуля симуляции тактового сигнала с частотой в 100 MHz.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following library declaration if instantiating

-- any Xilinx leaf cells in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

--// для тестбенча внешних портов не требуется

entity testbench is

-- Port ( );

end testbench;

--// реализация архитектуры

architecture Behavioral of testbench is

--// подключение компонента invertor

component invertor

Port (

a:in std_logic;

b:out std_logic

);

end component;

--// инициализация внутренних сигналов

signal clk: std_logic:='1'; -- // начальное значение для тактирования

constant period:time:=10 ns; --// Период частоты тактирования симуляции 100MHz

signal output: std_logic; --// выход инвертированного сигнала

begin

--// Симуляция тактирования

clock_gen: process

begin

loop --// начало безконечного цикла

clk<=not clk; --// инверсия тактирования

wait for period/2; --// ожидание времени

end loop; --// конец безконечного цикла

end process;

--// создаем экземляра компонента для которого

example: invertor

port map(

a=>clk, --// ассоциируем тактовый сигнал с входом а

b=>output --// ассоциируем выходной сигнал с выходом b

);

end Behavioral;

Для testbench у entity не портов входа и выхода, т.к. по сути это и есть наша ПЛИС. Т.к. это самый главный черный ящик, поэтому мы его и настраиваем как Top. Тактирование мы симулируем в блоке clock: process. Для того чтобы инверсия работала нужно не забыть у начального сигнала при инициализации задать начальное значение '0' или '1', т.к. по-умолчанию логический уровень неизвестен. Для того чтобы подключить наш модуль, который мы собираемся тестировать необходимо в начале подключить его реализацию, а далее мы создаем экземпляры и ассоциируем его входы и выходы с сигналами от других модулей.

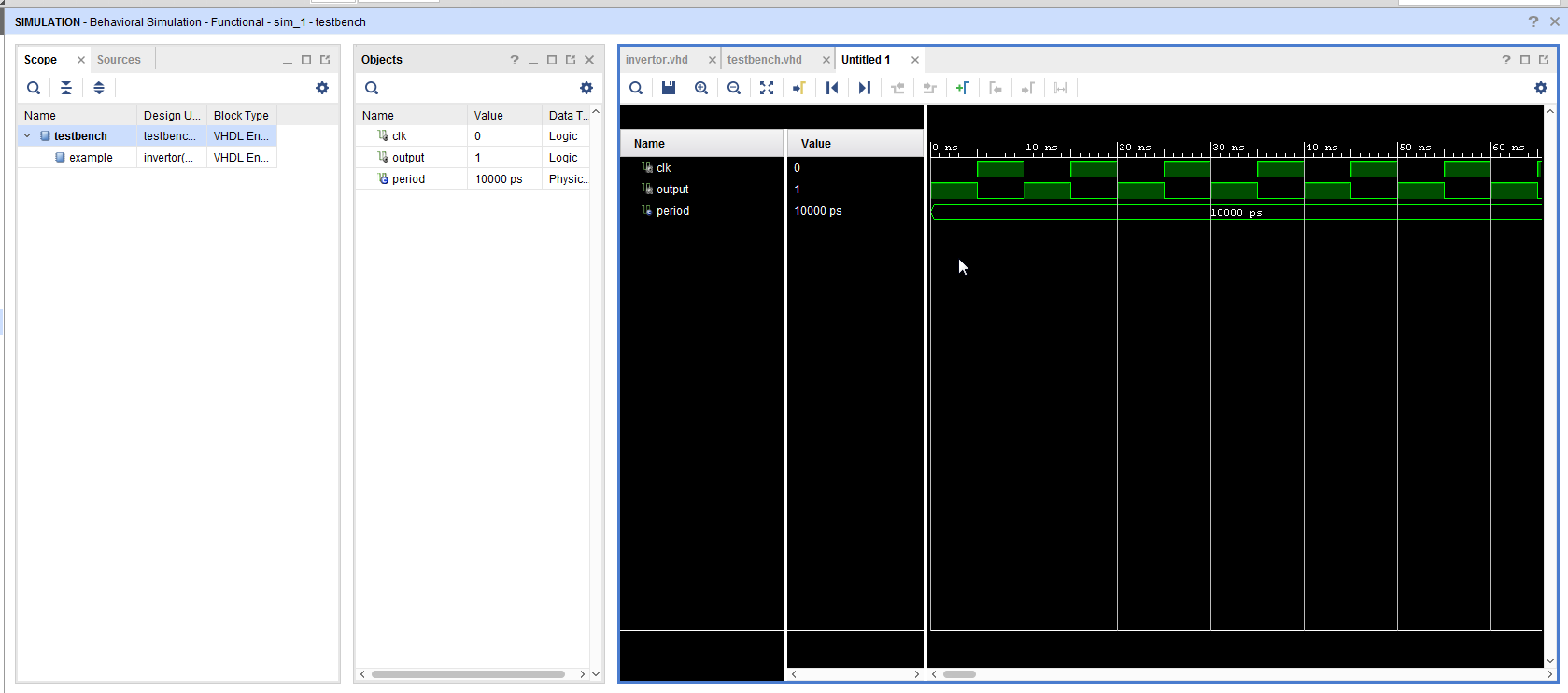

После того, как мы подключили тестируемый экземпляр к тактированию, можно нажать на кнопку Run Simulation, получим следующую картину симуляции

Как видим выход инвертирован относительно тактирующего сигнала.

В статье я постарался по шагам показать весь путь создания проекта, разработки шаблона основного модуля и testbench для проверки его работы. Я не стал останавливаться на описании конструкций языка VHDL, компенсируя это комментариями.

Прикрепленные файлы:

- clock_test.rar (47 Кб)

Опубликована:

Опубликована:

Вознаградить

Вознаградить

Комментарии (1) |

Я собрал (0) |

Подписаться

|

Я собрал (0) |

Подписаться

Для добавления Вашей сборки необходима регистрация