Систему ввода-вывода микроконтроллеров AVR можно считать одной из самых сильных сторон архитектуры. Каждая линия допускает независимое управление, имеет симметричные нагрузочные характеристики и номинальные втекающий и вытекающий токи до 20…25 мА (максимальный до 40 мА) с просадкой напряжения не более 0.7 В.

Линии объединяются в 8-разрядные порты ввода-вывода, которые у AVR имеют названия A,B,C…K,L. Обозначение каждой линии на схеме определяет ее принадлежность к порту и порядковый номер. Например, выводы порта B имеют названия PB0,PB1…PB7, порта D - PD0,PD1…PD7 и т.д. В различных моделях отдельные порты могут содержать меньше 8 линий ввода-вывода.

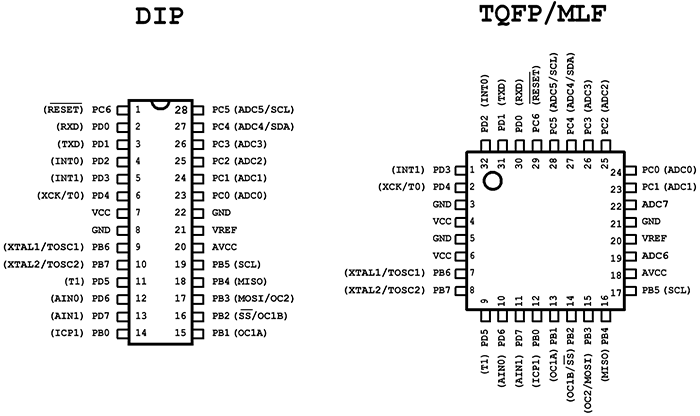

Рис.11 Расположение выводов ATmega8

Большинство выводов AVR-микроконтроллеров имеют также альтернативные назначения. Это аналоговые линии компаратора и АЦП, цифровые модулей SPI, TWI, USART и т.д. Описание выводов микроконтроллера ATmega8 находится в табл.6, а схема их расположения на рис.11.

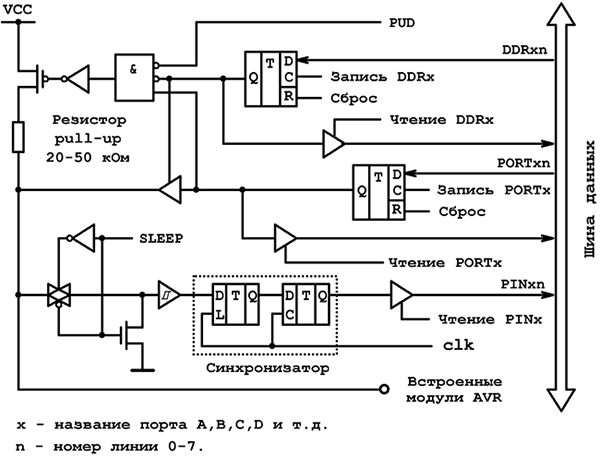

Рис.12 Внутрення схема линии порта ввода-вывода

Упрощенная внутренняя схема линии порта ввода-вывода приведена на рис.12. Каждым портом микроконтроллера управляют 3 РВВ. Это DDRx, PORTx и PINx (x – название порта: A,B,C и т.д.). Регистры портов A,B,C,D всех моделей находятся в первой половине адресного пространства ввода-вывода и поэтому допускают прямые операции над отдельными их битами. В цифровых портах AVR реализована истинная функциональность “чтение-модификация-запись”.

Регистр DDRx отвечает за направление передачи данных. Запись лог.1 в разряды DDRx настраивает линии на вывод, а запись лог.0, соответственно, на ввод. Например:

ldi R16,0b11100011 ;настроить на ввод линии 2,3,4 и

out DDRB,R16 ;на вывод линии 0,1,5,6,7 порта B

sbi DDRB,0 ;настроить на вывод линию 0 порта B

cbi DDRB,1 ;настроить на ввод линию 1 порта B

Регистр PORTx имеет двойное предназначение. Если линии порта настроены на вывод, то содержимое PORTx определяет логическое состояние выводов порта. Для линий настроенных на ввод значение PORTx определяет состояние внутреннего подтягивающего (pull-up) резистора к шине питания. В этом случае при уровне лог.1 в разрядах PORTx резистор подключен, а при уровне лог.0 – отключен и линии переведены в высокоимпедансное состояние (z-состояние):

ldi R16,0b11110000 ;настроить на вывод линии 4…7

out DDRC,R16 ;и на ввод линии 0…3 порта С

ldi R16,0b11111111 ;выставить на линиях 4…7 порта С уровень лог.1

out PORTC,R16 ;и подключить к линиям 0…3 порта С pull-up резисторы

sbi DDRC,0 ;настроить на вывод линию 0 порта C

cbi PORTC,0 ;выставить на линии 0 порта С уровень лог.0

сbi DDRC,1 ;настроить на ввод линию 1 порта C

сbi PORTC,1 ;перевести линию 1 порта С в z-состояние

Регистр PINx предназначен для считывания уровней сигнала с выводов микроконтроллера. Естественно, что необходимость в этом существует только для линий настроенных на ввод (для линий настроенных на вывод содержимое PINx повторяет состояние выходного регистра PORTx). Разряды PINx не оказывают ни какого влияния на состояние выводов, а сам регистр доступен только для чтения. Логический уровень входной линии фиксируется в триггере-защелке в каждом цикле тактовой частоты. Таким образом, реальное значение сигнала при считывании может иметь отставание порядка 0.5…1.5 машинных циклов. Пример использования:

cbi DDRD,0 ;настроить на ввод линию 0 порта D sbi PORTD,0 ;подключить к линии 0 порта D pull-up резистор nop ;задержка 1 цикл для установки режима sbis PIND,0 ;считать состояние линии 0 порта D rjmp ulo ;если лог.0, то перейти на метку ulo rjmp uhi ;если лог.1, то перейти на метку uhi

У микроконтроллеров AVR имеется возможность управлять pull-up резисторами сразу на всех его выводах. За это свойство отвечает бит PUD из РВВ SFIOR либо MCUCR. При установке разряда PUD запрещается подключение всех резисторов. При PUD=0 (значение после сброса) состояние внутренних резисторов определяется состоянием регистра PORTx.

Различные возможности конфигурации линий портов ввода-вывода AVR приведены в табл.7. На время спящего режима (после выполнения команды sleep) входной буфер порта отключается.

При использовании выводов микроконтроллера по их альтернативному назначению, может понадобится вручную сконфигурировать линии. Так, например, в случае применения компаратора, АЦП, внешних прерываний соответствующие линии должны быть переведены в z-состояние, а для ШИМ-выводов таймеров счетчиков и выходных сигналов других модулей линии должны быть настроены на вывод.

Табл.6. Описание выводов модели ATmega8(L):

|

Номер вывода в корпусе DIP-28 |

Номер вывода в корпусах |

Функция вывода |

Описание |

|

14 |

12 |

PB0 |

0-й бит порта B |

|

ICP1 |

Вход захвата таймера-счетчика 1 |

||

|

15 |

13 |

PB1 |

1-й бит порта B |

|

OC1A |

ШИМ-вывод A таймера-счетчика 1 |

||

|

16 |

14 |

PB2 |

2-й бит порта B |

|

OC1B |

ШИМ-вывод B таймера-счетчика 1 |

||

|

SS |

Вывод Slave нашине SPI |

||

|

17 |

15 |

PB3 |

3-й бит порта B |

|

OC2 |

ШИМ-вывод таймера-счетчика 2 |

||

|

MOSI |

Выход Master или вход Slave данных на шине SPI |

||

|

18 |

16 |

PB4 |

4-й бит порта B |

|

MISO |

Вход Master или выход Slave данных на шине SPI |

||

|

19 |

17 |

PB5 |

5-й бит порта B |

|

SCK |

Выход Master или вход Slave тактового сигнала модуля SPI |

||

|

9 |

7 |

PB6 |

6-й бит порта B |

|

XTAL1 |

Вывод тактового генератора |

||

|

TOSC1 |

Вывод для подключения резонатора к таймеру-счетчику 2 |

||

|

10 |

8 |

PB7 |

7-й бит порта B |

|

XTAL2 |

Вывод тактового генератора |

||

|

TOSC2 |

Вывод для подключения резонатора к таймеру-счетчику 2 |

||

|

2 |

30 |

PD0 |

0-й бит порта D |

|

RXD |

Вход USART |

||

|

3 |

31 |

PD1 |

1-й бит порта D |

|

TXD |

Выход USART |

||

|

4 |

32 |

PD2 |

2-й бит порта D |

|

INT0 |

Вход внешнего прерывания 0 |

||

|

5 |

1 |

PD3 |

3-й бит порта D |

|

INT1 |

Вход внешнего прерывания 1 |

||

|

6 |

2 |

PD4 |

4-й бит порта D |

|

XCK |

Вход/выход внешнего тактового сигнала модуля USART |

||

|

T0 |

Вход/выход внешнего тактового сигнала таймера-счетчика 0 |

||

|

11 |

9 |

PD5 |

5-й бит порта D |

|

T1 |

Вход/выход внешнего тактового сигнала таймера-счетчика 1 |

||

|

12 |

10 |

PD6 |

6-й бит порта D |

|

AIN0 |

Неинвертирующий вход компаратора |

||

|

13 |

11 |

PD7 |

7-й бит порта D |

|

AIN1 |

Инвертирующий вход компаратора |

||

|

23 |

23 |

PC0 |

0-й бит порта C |

|

ADC0 |

0-й вход АЦП |

||

|

24 |

24 |

PC1 |

1-й бит порта C |

|

ADC1 |

1-й вход АЦП |

||

|

25 |

25 |

PC2 |

2-й бит порта C |

|

ADC2 |

2-й вход АЦП |

||

|

26 |

26 |

PC3 |

3-й бит порта C |

|

ADC3 |

3-й вход АЦП |

||

|

27 |

27 |

PC4 |

4-й бит порта C |

|

ADC4 |

4-й вход АЦП |

||

|

SDA |

Вход/выход данных модуля TWI |

||

|

28 |

28 |

PC5 |

5-й бит порта C |

|

ADC5 |

5-й вход АЦП |

||

|

SCL |

Вход/выход тактового сигнала модуля TWI |

||

|

1 |

29 |

PC6 |

6-й бит порта C |

|

RESET |

Вход сброса |

||

|

- |

19 |

ADC6 |

6-й вход АЦП |

|

- |

22 |

ADC7 |

7-й вход АЦП |

|

8,22 |

3,5,21 |

GND |

Общий вывод |

|

21 |

20 |

VREF |

Вход опорного напряжения для АЦП |

|

20 |

18 |

AVCC |

Вывод источника питания АЦП |

|

7 |

4,6 |

VCC |

Вывод источника питания микроконтроллера |

Табл.7. Конфигурация выводов порта:

|

DDRxn |

PORTxn |

PUD |

Функция вывода |

Резистор |

Примечание |

|

0 |

0 |

X |

Вход |

Отключен |

На выводе z-состояние |

|

0 |

1 |

0 |

Вход |

Подключен |

На выводе присутствует положительное смещение к источнику питания |

|

0 |

1 |

1 |

Вход |

Отключен |

На выводе z-состояние |

|

1 |

0 |

X |

Выход |

Отключен |

На выводе лог.0 |

|

1 |

1 |

X |

Выход |

Отключен |

На выводе лог.1 |

Перейти к следующей части: Система команд - Способы адресации

Котов Игорь Юрьевич

Котов Игорь Юрьевич

Опубликована: 2012 г.

Опубликована: 2012 г.

Вознаградить

Вознаградить

Комментарии (1) |

Я собрал (0) |

Подписаться

|

Я собрал (0) |

Подписаться

Для добавления Вашей сборки необходима регистрация