Хочу в очередной раз поделиться своей разработкой. На этот раз - частотомер. Не самое бесполезное устройство для радиолюбителя, особенно для любителей цифровой электроники.

В сети много подобных устройств на разнообразной элементной базе: чаcто попадается схема на микроконтроллере PIC, попадались схемы и на дискретной логике и многие другие. Сердцем описываемого частотомера является CPLD Altera MAX II. Довольно интересная микросхема: стоит довольно дёшево (я ухватил на Ali десяток за 12 с мелочью долларов, правда, очевидно, бывшие в употреблении, но вполне рабочие), имеет на борту 240 логических ячеек, чего вполне достаточно для простых устройств или замены кучи дискретной логики, частота работы до 200MHz, много программируемых внешних пинов. Есть и минусы - корпус TQFP100 с очень мелким шагом, не каждый сможет самостоятельно изготовить печатную плату под такой корпус, отсутствуют специализированные блоки (такие как PLL, ячейки RAM), а также необходимость в программаторе.

Расскажу немного об основных элементах устройства. Результат измерения частоты отображается на семи сегментных светодиодных индикаторах. В конкретном приборе это два трёхразрядных индикатора с общим катодом (советские, И38А-К КО). Индикация динамическая, частота индикации 512 Гц (по 56Hz на разряд, кстати, измерена этим же частотомером), чего вполне достаточно для отображения без мерцания, хотя при желании можно изменить частоту, подправив пару строк в конфигурации.

Так как CPLD работает от 3,3 вольт и имеет соответствующие логические уровни, в схему добавлен входной буфер на микросхеме 74LVC245 - это восьми разрядный двунаправленный буфер КМОП, который питается от 3,3 вольта, но может принимать на вход до 6 вольт.

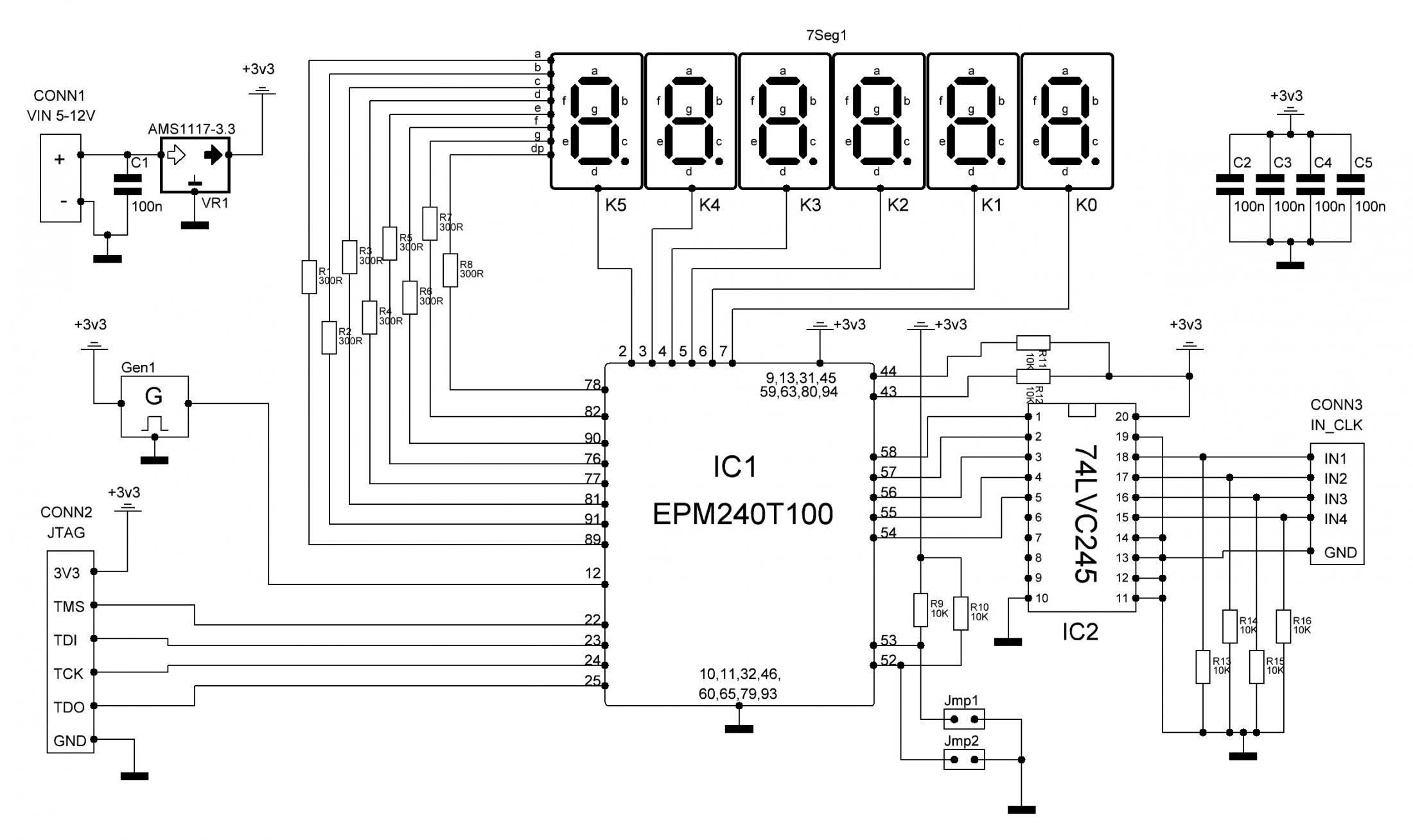

Кроме этого в схеме присутствует минимальный набор обвязки для CPLD: кварцевый генератор, стабилизатор питания на 3,3 вольта, а также резисторы и конденсаторы. Смотрите принципиальную схему:

Схема достаточно условная, так как благодаря гибкости CPLD можно настраивать практически любой пин к необходимой части внутренней схемы (за это я очень люблю разводить платы под ПЛИС и CPLD). На этой схеме отображено подключение CPLD именно так, как на моей плате. Но при необходимости поставить другой индикатор (больше разрядов) или дополнительные кнопки или светодиоды, то они могут подключаться к любому свободному пину микросхемы (кроме пинов питания, программирования и тактирования). Также их можно менять местами как угодно. Отмечу только, что схема немного избыточна: в ней имеется четыре входа для счёта импульсов, подключенные через входной буфер - это сделано "на всякий случай" и из-за того, что жалко использовать только один буфер из восьми имеющихся в 74LVC245. Также имеются два джампера для переключения режимов индикации частоты.

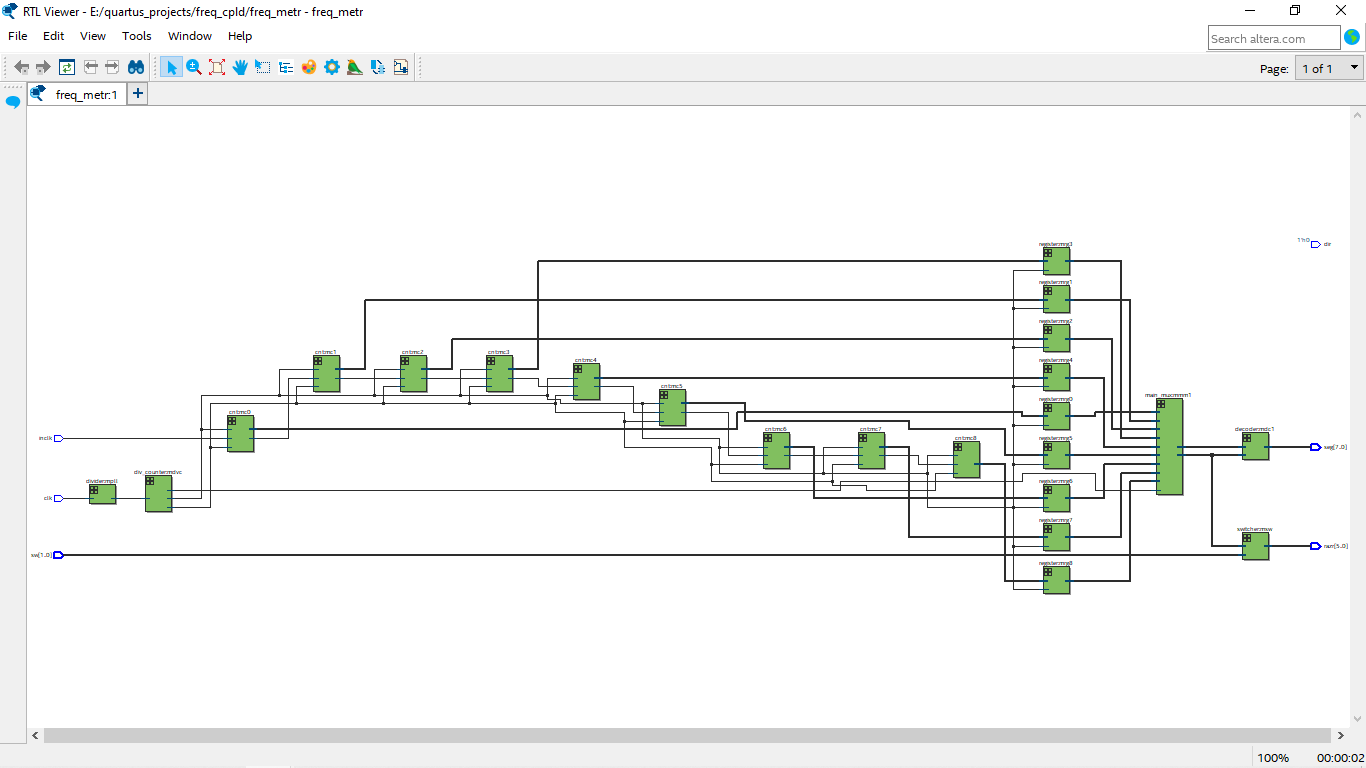

Принципиальная схема довольно простая, но это только верхушка айсберга. Основная схема конфигурируется внутри CPLD. Конфигурация написана на языке Verilog HDL (это язык описания цифровых схем в текстовом виде, для тех, кто не в теме), поэтому привычной схемы в виде логических элементов, вентилей, счётчиков не будет. А для наглядности я приведу структурную схему из Quartus IDE:

На первый взгляд - набор каких то прямоугольников, соединённых проводами. Но попытаюсь объяснить: на входе CLK (который подключен к задающему кварцевому генератору) подключены два счётчика делителя опорной частоты. Далее идёт каскад из счётчиков, которые умеют считать от нуля до девяти, подключенные ко входу измерения частоты и имеют кроме счётного входа, вход сброса, вход разрешения счёта и выход переноса. К выходу каждого счётчика подключены регистры-защёлки. Каждая защёлка подключена к главному мультиплексору динамической индикации. А на его выходе стоит дешифратор семи сегментного кода. Также на этой блок-схеме на выходах разрядов индикатора добавлен блок сдвига сегментов (это необязательный блок, добавлен для удобства отображения частоты), подключенный к джамперам Jp1 и Jp2.

Принцип работы следующий: тактовая частота опорного генератора делится первым делителем до 256 Гц для формирования секундного интервала (удалось поделить 40MHz без остатка только до 512) и приблизительно до 500Гц для тактирования динамической индикации (пришлось делать по сути два делителя внутри этого модуля, так как 256Гц не достаточно для динамической индикации девяти сегментов, они очень сильно мерцают). Затем вторым делителем опорная частота делится до 0,5 Гц. Частота 500Гц подаётся на мультиплексор динамической индикации, а 0,5Гц вместе с её инвертированным сигналом подаются на входы разрешения счёта "двоично-десятичных" счётчиков, на входы их сброса и на регистры защёлки. Сигнал для счёта импульсов (inclk) подключен к счётному входу первого десятичного счётчика (младшего разряда), остальные двоично-десятичные счётчики подключены последовательно - счётный вход следующего подключен к выводу переноса предыдущего. По низком уровню импульса в 0,5Гц каскад счётчиков начинает считать импульсы (ровно одну секунду), а по восходящему фронту частоты 0,5 Гц - результаты счёта из счётчиков записываются в регистры, а значения самих счётчиков, обнуляются. Далее значения регистров попадают в мультиплексор динамической индикации, который на своей частоте поочередно выводит значение нужного регистра на выход и поочерёдно подаёт сигналы на нужный катод индикатора. На выходе мультиплексора стоит дешифратор семи сегментного кода, который преобразует двоичное значение (4-бита) в соответствующие значения для анодов семисегментников (8-бит). Также в нём отдельно декодируется десятичная точка, которая отделяет значения "целых Мегагерц" от их дробного значения - просто, для удобного отображения. Дополнительный блок сдвига сегментов на выходе катодов индикатора "сдвигает" отображение разрядов по индикатору в зависимости от установленных джамперов на входе sw[1:0] (так как индикатор у меня шестиразрядный, а значение частоты может быть до 9 знаков - "сотни" мегагерц). Как-то так, если вкратце.

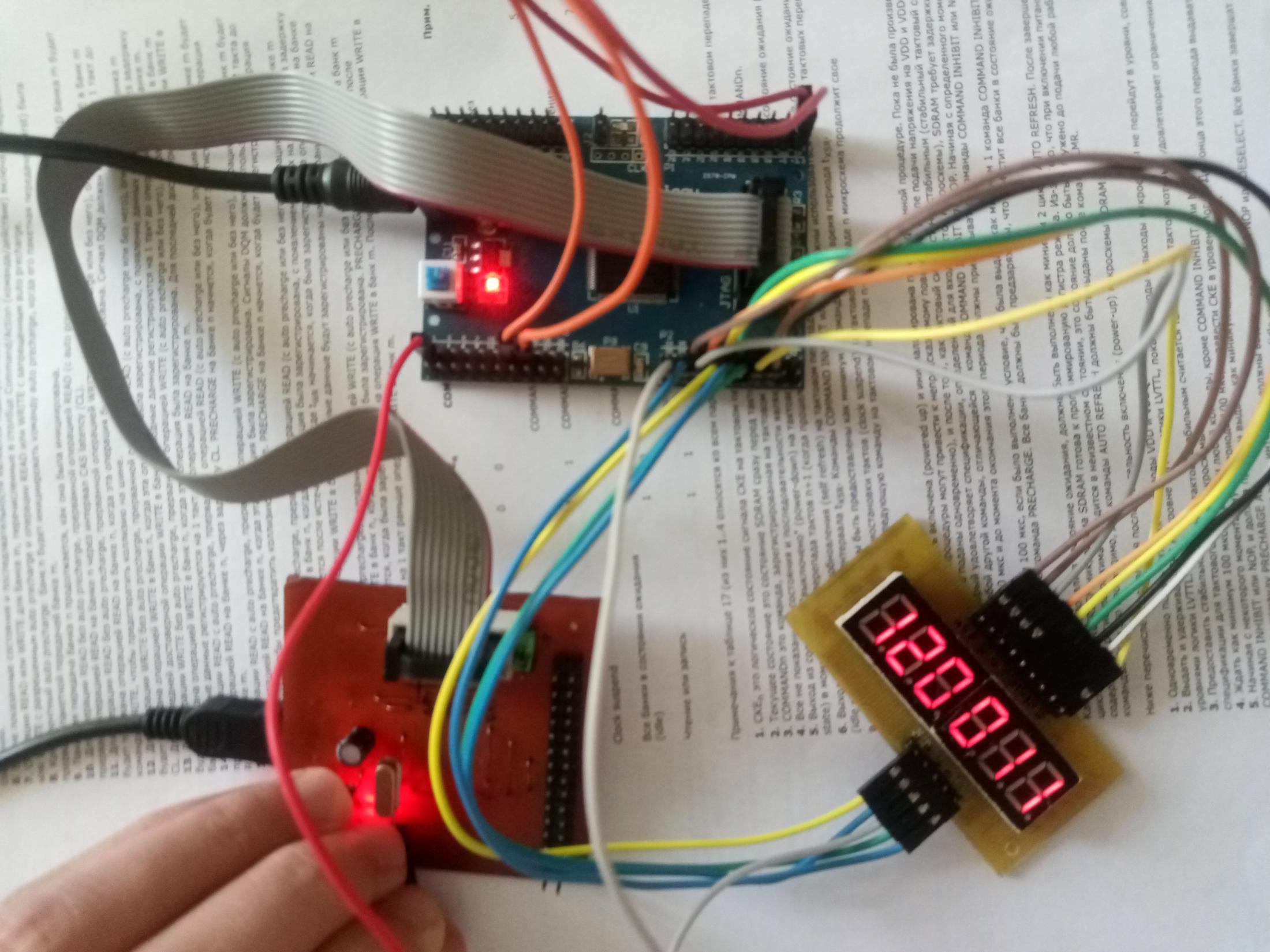

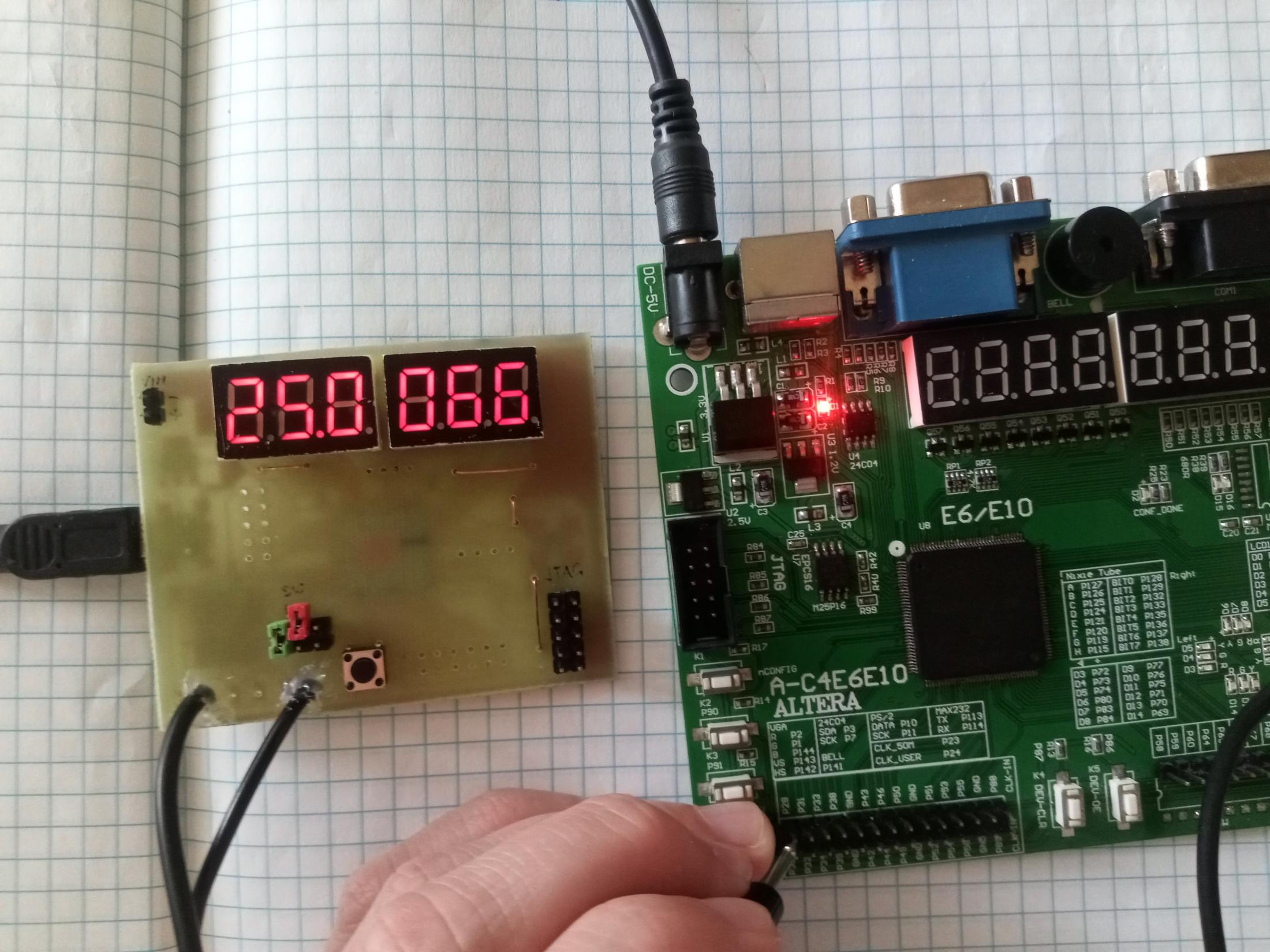

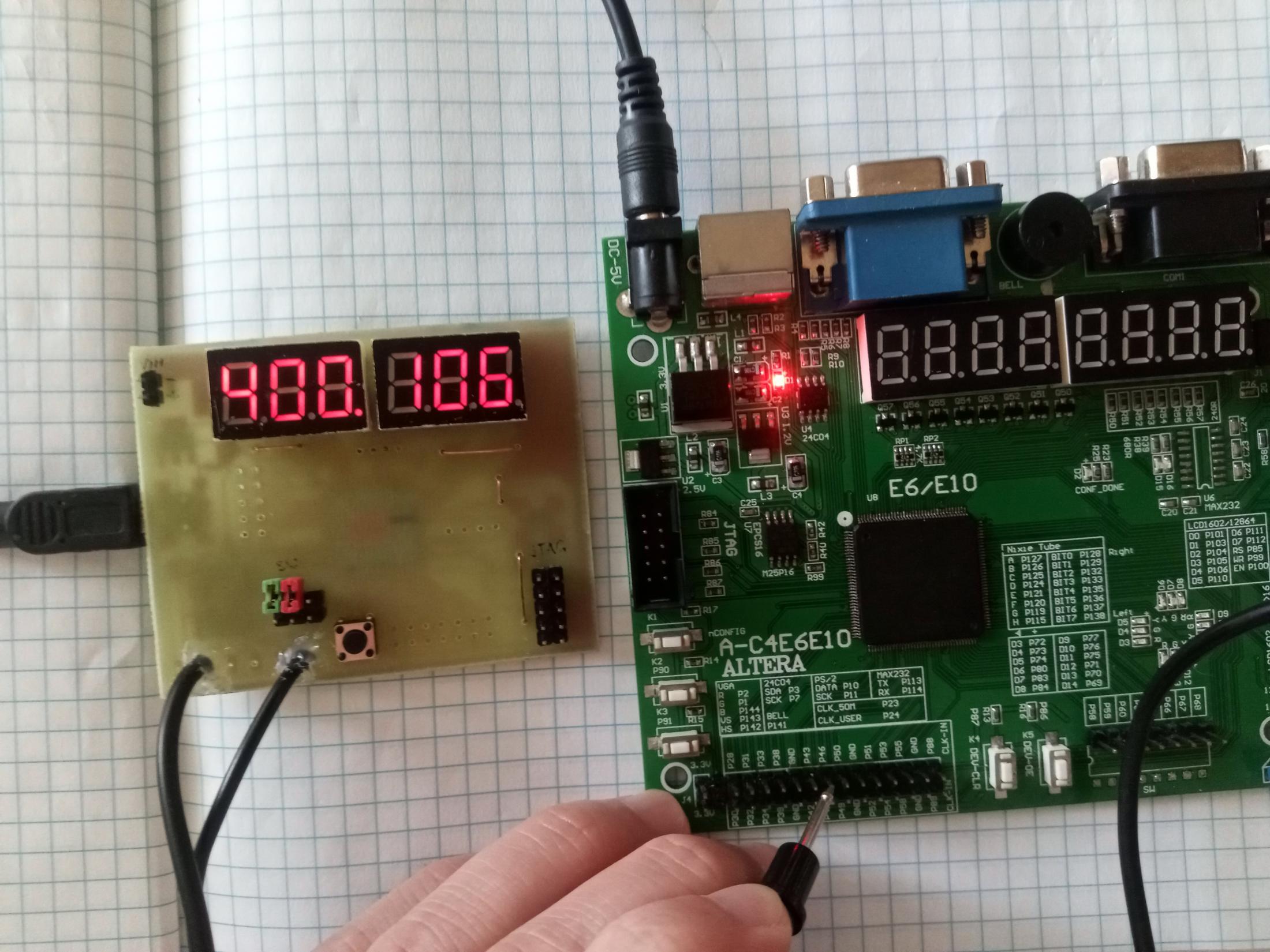

Перед изготовлением устройства в железе (в окончательном виде) я его отлаживал на макетной плате с идентичной CPLD и кучей проводков. Выглядело это так:

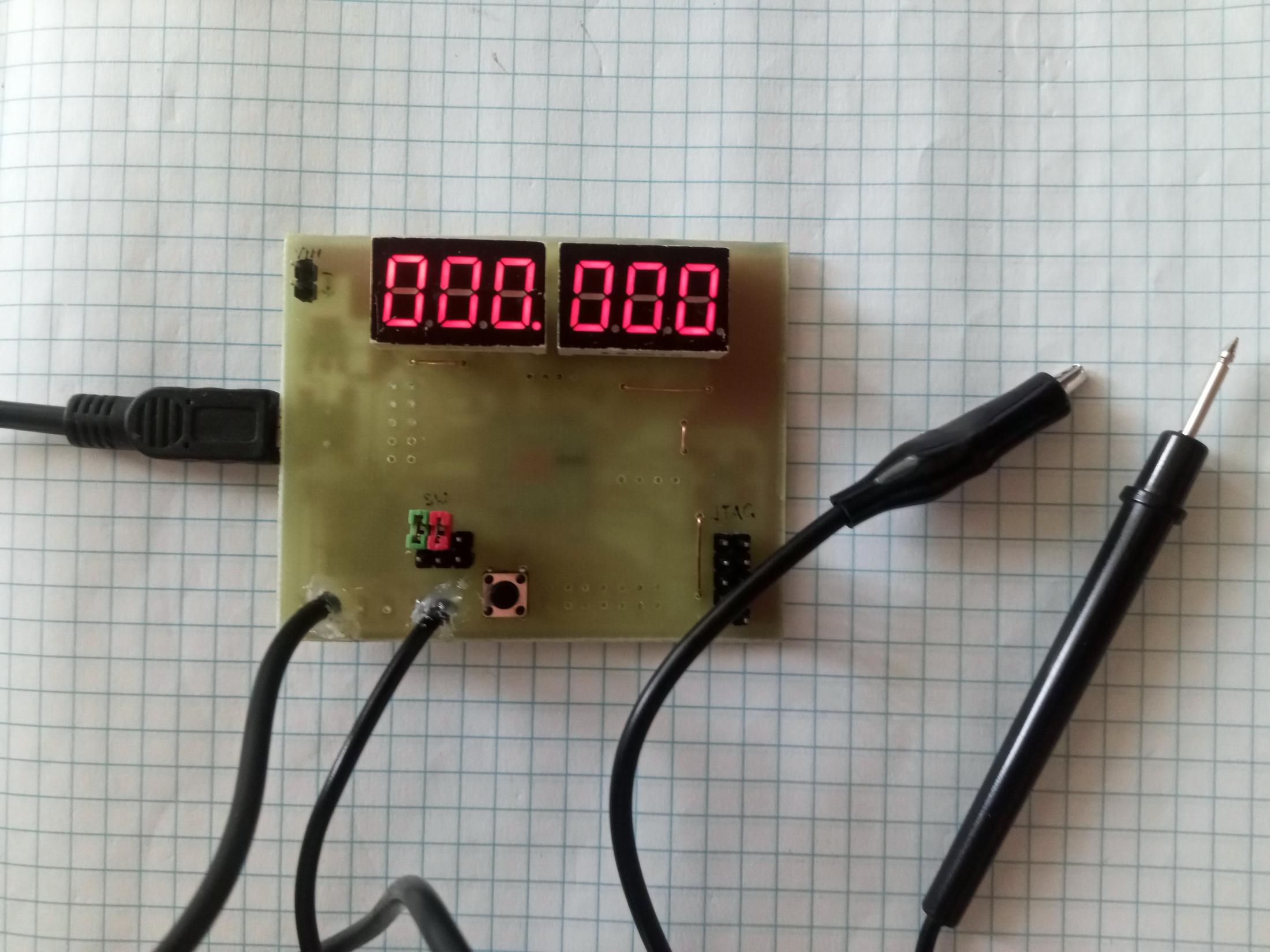

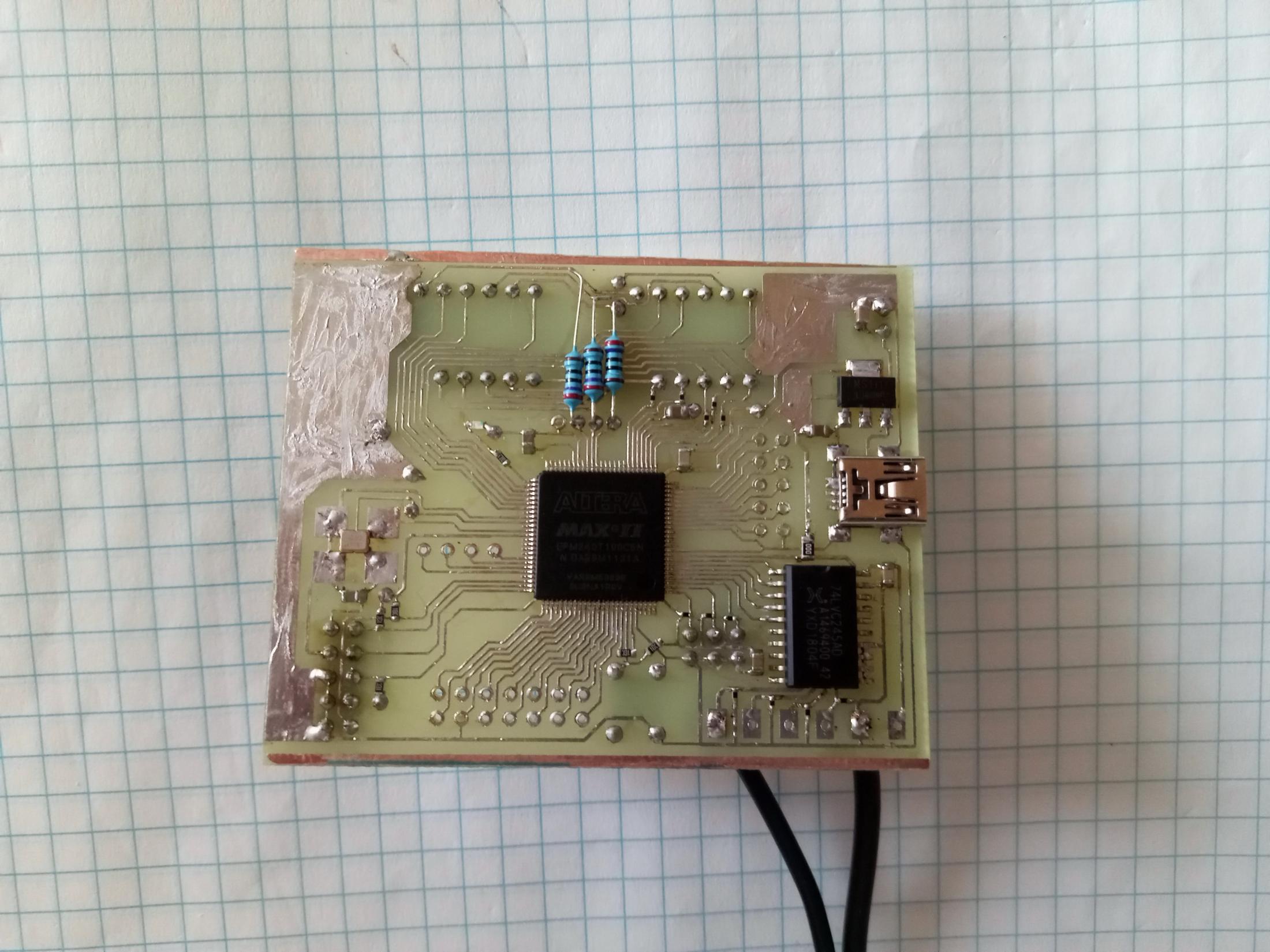

Отладив всё на макетке, устройство было реализовано в конечном виде:

Как всегда немножко накосячил с разводкой платы, забыл подключить три сегмента индикаторов, поэтому пришлось навешать обычных резисторов. Хорошо, что когда разводил плату, на всякий случай развёл запасные пины, вот и пригодились. Также на плате разведены несколько "не нужных" разъёмов, на которые выведены незадействованные пины, на случай других экспериментов с платой, да и жалко, что столько "добра пропадает" без толку. В том числе есть "запасной" третий джампер. Кнопка на плате - сброс CPLD, тоже - необязательная. На разъём входа измерения в том числе выведены плюс и минус на случай подключения внешнего активного щупа (в файле Sprint Layout я постарался всё подписать). В окончательной версии платы все ошибки исправлены.

Как всегда немножко накосячил с разводкой платы, забыл подключить три сегмента индикаторов, поэтому пришлось навешать обычных резисторов. Хорошо, что когда разводил плату, на всякий случай развёл запасные пины, вот и пригодились. Также на плате разведены несколько "не нужных" разъёмов, на которые выведены незадействованные пины, на случай других экспериментов с платой, да и жалко, что столько "добра пропадает" без толку. В том числе есть "запасной" третий джампер. Кнопка на плате - сброс CPLD, тоже - необязательная. На разъём входа измерения в том числе выведены плюс и минус на случай подключения внешнего активного щупа (в файле Sprint Layout я постарался всё подписать). В окончательной версии платы все ошибки исправлены.

Работать с частотомером очень просто: подаём питание, подключаем "минусовой" щуп на землю устройства, где будем измерять частоту и ставим "плюсовой" щуп в нужную точку платы. Ничего сложного, практически никаких настроек, кроме двух джамперов. Джамперы работают следующим образом: при разомкнутых обоих джамперах отображается значение частоты с 9 по 4 десятичный разряд (т.е. сотни мегагерц, обрезается три последних знака сотен герц), если установлена перемычка на Jp1 - отображаются разряды с 8 по 3, при установленном Jp2 отображаются разряды с 7 по 2, и при установленных Jp1 и Jp2 отображаются шесть младших разрядов. При этом точка, отделяющая мегагерцы от их дробных значений тоже сдвигается, соответственно при установленных обоих джамперах точки нет. Джамперы можно менять на лету, это абсолютно не влияет на измерение частоты, только меняет её отображение на индикаторе.

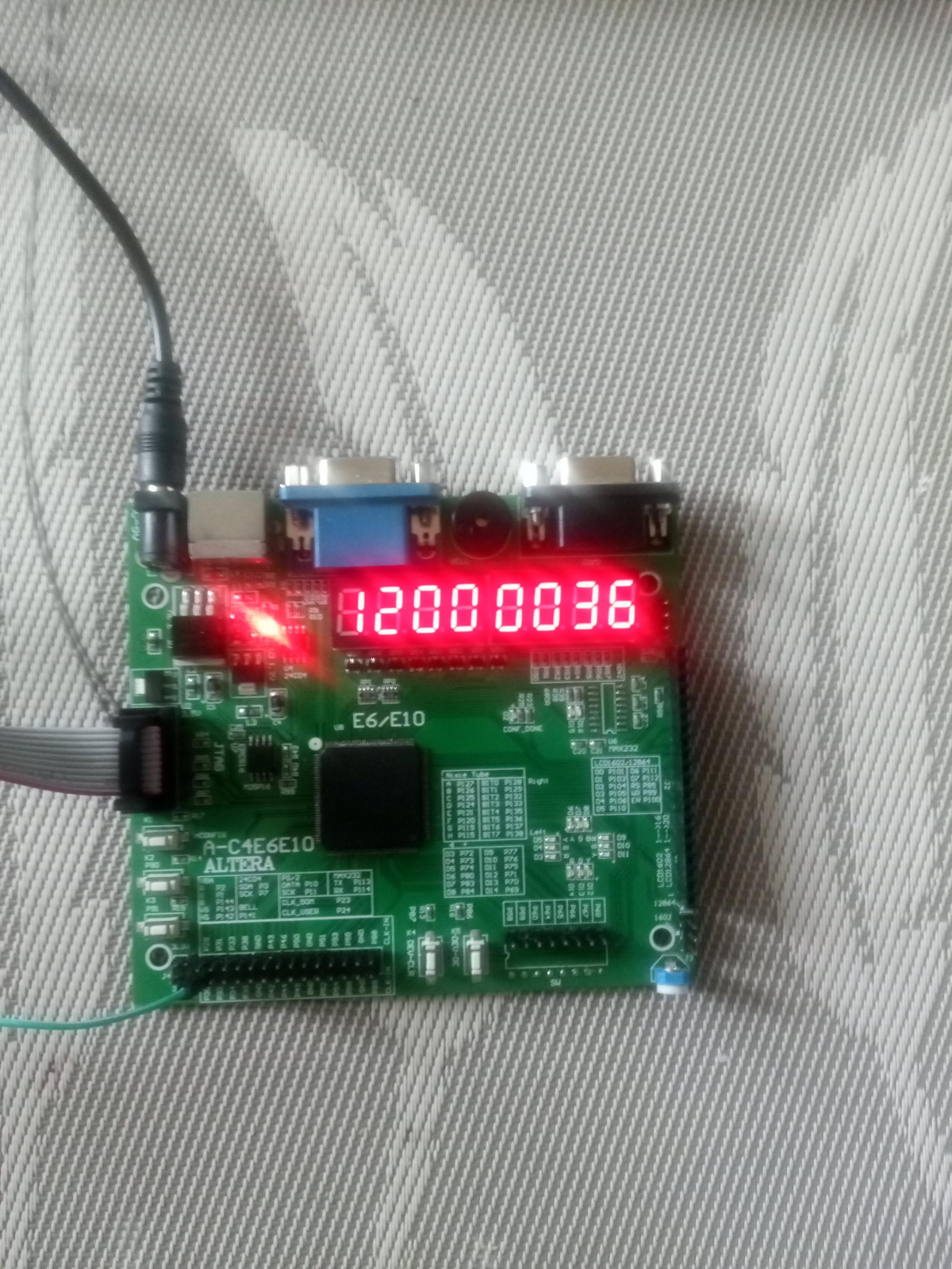

Так как генератора сигналов или генератора частоты у меня нет, для проверки работы я использовал макетную плату с FPGA Altera Cyclone 4 (на Алиэкспресс), на этой плате с помощью встроенных модулей PLL можно синтезировать разнообразные частоты, как низкие, так и высокие. Внешний вид платы:

Так как у моей CPLD по документации максимальная частота работы до 200MHz, да и у входного буфера на LVC245 тоже есть своя максимальная частота, то логично предположить, что это будет максимальная частота измерения частотомера. Забегая вперёд, скажу, я проверил частоты до 400MHz, которые я синтезировал на ПЛИС. Сигналы были, естественно, прямоугольной формы. И он с ними справился! Измерения были достаточно стабильными.

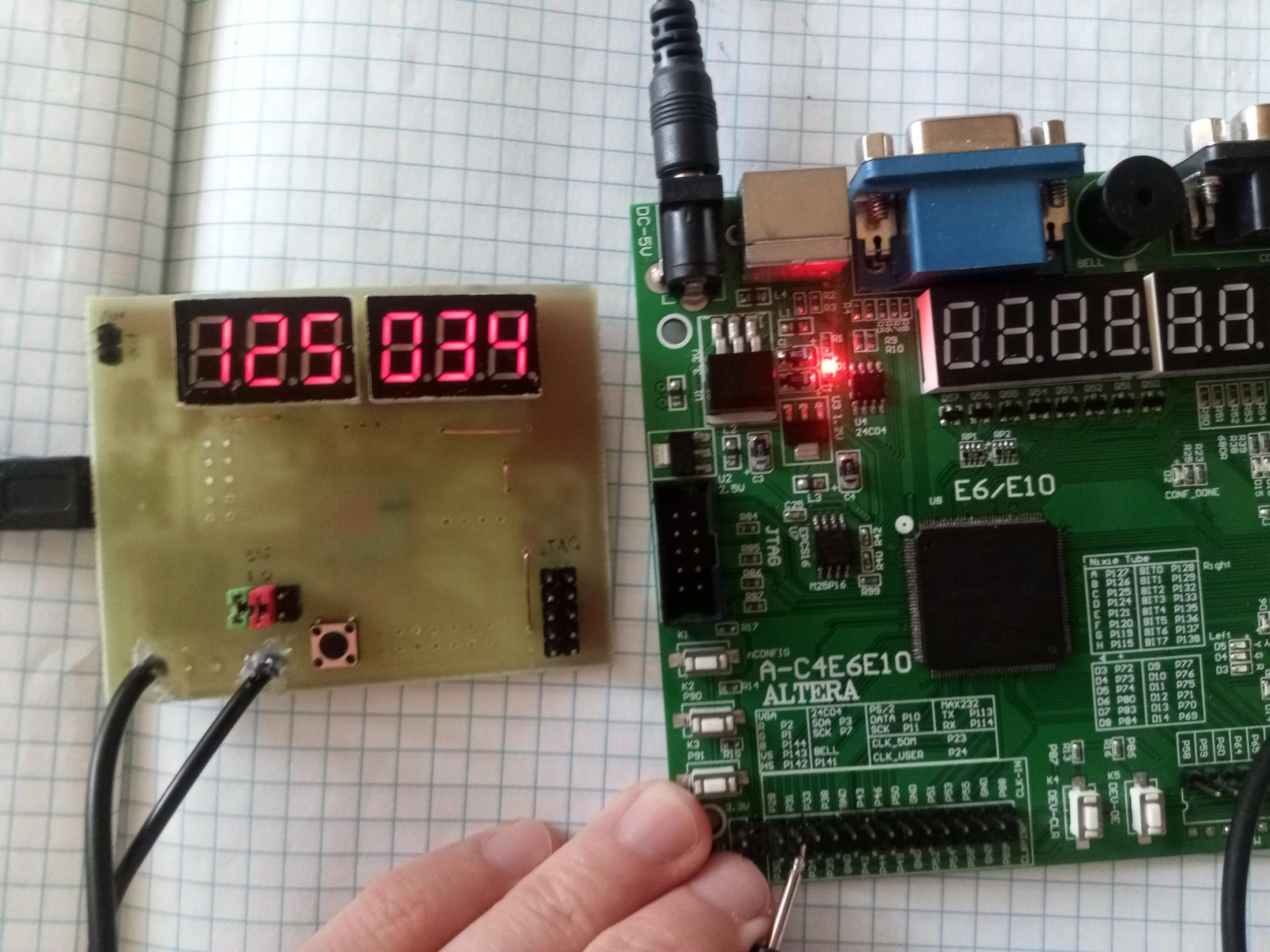

125KHz:

1MHz (обратите внимание на джамперы и десятичную точку на индикаторе):

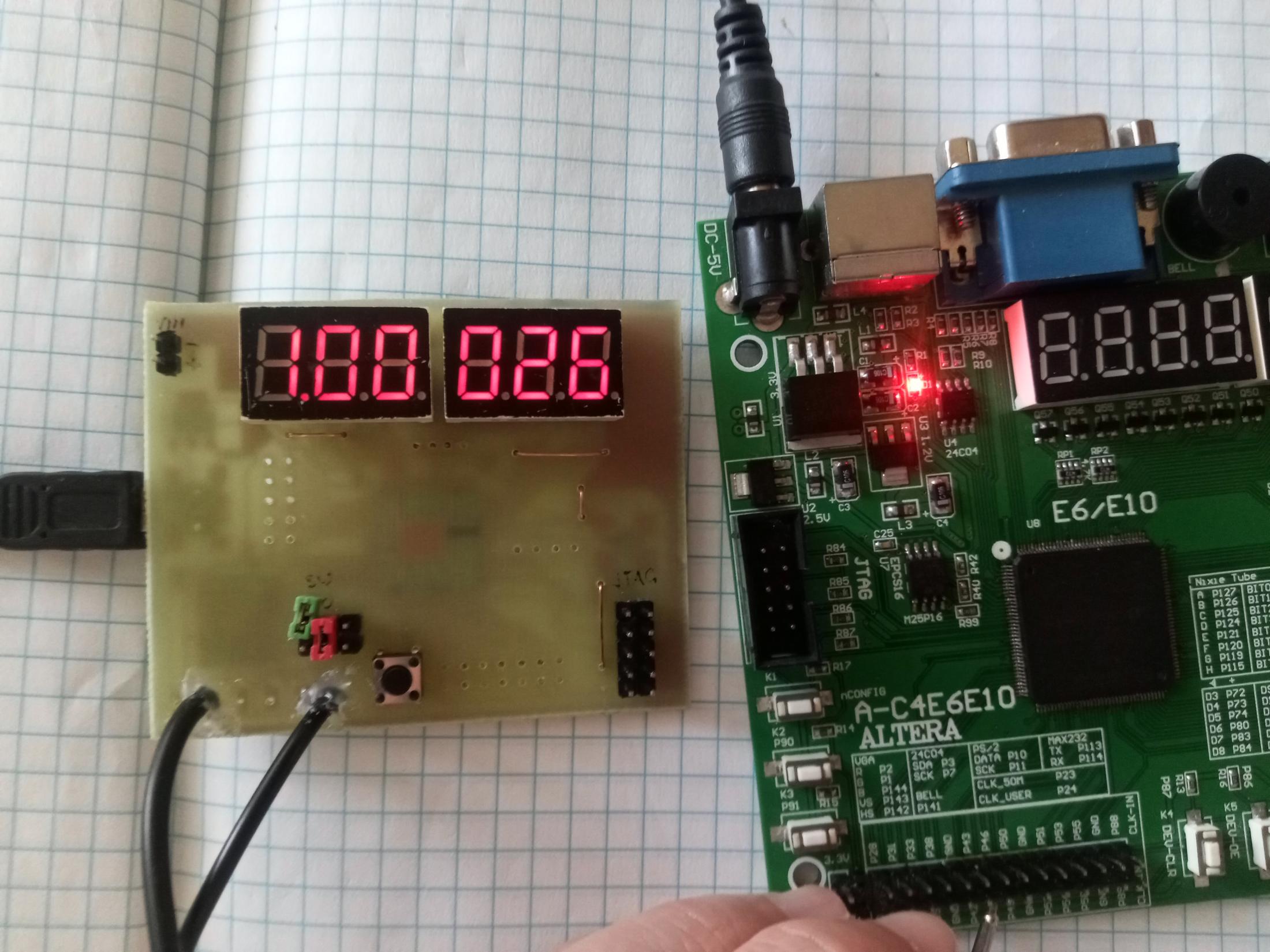

25MHz:

400MHz:

Отмечу, что фото работы делались на промежуточном этапе отладки устройства. Поэтому можно заметить большую погрешность измерения. Она связана с тем, что изначально проект частотомера я писал для ПЛИС (той, которая изображена на фото выше, кстати, на фото на ней сконфигурирован этот проект) и пытался его адаптировать "в лоб" для CPLD. А в ПЛИС в отличие от CPLD имеются модули PLL. На PLL я синтезировал частоту часового кварца 32768Гц и её я делил до 0,5Гц. На CPLD такого модуля нет. И я пытался получить эту частоту простым делением. Погрешность получалась примерно 0,025%.

Потом я немного поработал с калькулятором и нашел нужное целое кратное 8 значение до которого делится 40 мегагерц кварцевого генератора - это значение 512. Таким образом при инвертировании одного регистра 512 раз в секунду получилась частота 256Гц, из которой делением простым двоичным счётчиком можно получить "эталонную" секундную задержку. Таким образом точность измерения зависит только от точности опорной частоты кварцевого генератора. Что доказывается измерением частоты генератора на "самом себе" - результат получился ровно 40,000,000 Гц.

Напоследок хочу сказать, что устройство, конечно, не претендует на звание "супер сложного" или "незаменимого", но его разработка и наладка принесла мне массу положительных эмоций. Считаю, время потрачено не зря. А для желающих повторить устройство - это отличный способ присоединиться к любителям ПЛИС, если до этого не работали с ними. Работать с ними очень интересно.

Как всегда, делюсь всеми файлами устройства: плата в Sprint Layout, проект в Quartus Prime, файл прошивки. На плате в Sprint все элементы подписаны или на "маске", или в свойствах компонентов. Smd резисторы нарисованы макросами конденсаторов (просто они меньше и больше подходят по размерам, чем макросы резисторов).

При желании, проект легко адаптируется под любую CPLD или ПЛИС, так как он написан на Verilog и не использует специфических модулей.

Для тех, кого останавливает отсутствие программатора: Прошить CPLD можно как специализированными программаторами (на Ali клон Altera USB Blaster стоит до 3$), так и при помощи обычной FT232(с любым индексом) и специальной программы "SVF-плеер" (не сложно найти в сети, по крайней мере CPLD от Xillinx я пробовал так прошивать). Сам я использую самодельный программатор Digilent на FT2232 (очень удобная штука, шьёт и Altera, и Xillinx).

Список радиоэлементов

| Обозначение | Тип | Номинал | Количество | Примечание | Магазин | Мой блокнот |

|---|---|---|---|---|---|---|

| IC1 | Микросхема | EPM240T100C5 | 1 | Поиск в магазине Отрон | ||

| IC2 | ИС шинного приемника, трансмиттера | SN74LVC245A | 1 | Поиск в магазине Отрон | ||

| VR1 | Линейный регулятор | AMS1117-3.3 | 1 | Поиск в магазине Отрон | ||

| Cr1 | Кварцевый генератор | 40MHz | 1 | Поиск в магазине Отрон | ||

| 7-Seg1,2 | Семисегментный индикатор | И38А-К | 2 | Можно любой | Поиск в магазине Отрон | |

| R9-R16 | Резистор | 10 кОм | 8 | Поиск в магазине Отрон | ||

| R1-R8 | Резистор | 300R | 8 | Поиск в магазине Отрон | ||

| C1-C5 | Конденсатор | 0.1 мкФ | 5 | Керамика | Поиск в магазине Отрон | |

Скачать список элементов (PDF)

Прикрепленные файлы:

- board.zip (38 Кб)

- firmware.zip (3 Кб)

- quartus_project(1).zip (1108 Кб)

Опубликована:

Опубликована:

Вознаградить

Вознаградить

Комментарии (4) |

Я собрал (0) |

Подписаться

|

Я собрал (0) |

Подписаться

Для добавления Вашей сборки необходима регистрация