Промышленно выпускаемые простейшие цифровые схемы

Раздел 1. Схемы на базе триггеров

На основе триггеров строится множество других цифровых схем. Самые распространённые – регистры и счётчики.

Рассмотрим их.

1.1 Регистры

Регистры – это простейшие запоминающие устройства. Регистры бывают 2-х типов - хранения и сдвига. В свою очередь, регистры хранения бывают «прозрачные» (срабатывание) по уровню тактового сигнала либо синхронные (срабатывают по уровню).

В основе любого регистра лежит набор D-триггеров. Как правило, у регистров присутствуют только прямые выходы, инверсные встречаются достаточно редко.

Так, регистр хранения – некоторое кол-во триггеров с объединёнными тактовыми входами. Т.е. тактовый вход всегда один. Информационные входы триггеров представляют собой вход регистра, выходы триггеров – выходы регистра. Регистры хранения ещё называют параллельными регистрами, т.к. информация в них заносится одновременно (параллельно) во все разряды. Кол-во разрядов регистра в промышленно выпускаемых микросхемах составляет 2, 4, 6 или 8.

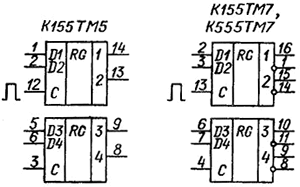

Например, микросхемы ТМ5 и ТМ7 – 2-разрядные регистры с записью высоким уровнем (прозрачные регистры), по 2 в корпусе – рис. 1.

Рис. 1

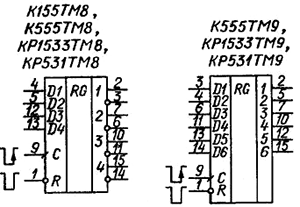

Некоторые микросхемы регистров имеют ещё и вход асинхронный вход сброса, позволяющий обнулить все разряды регистра – рис. 2.

Рис. 2

Регистры на рис. 2 уже динамические, т.е. запись в них происходит по нарастанию тактового сигнала.

Регистры сдвига могут сдвигать информацию, записанную в них.

Эти регистры всегда работают по фронту тактового сигнала.

Простейший регистр сдвига имеет вид – рис. 3.

Рис. 3. Простейший

регистр сдвига

Как видно из схемы, этот n-разрядный регистр имеет один инф. вход D, тактовый вход C и n выходов. Каждый тактовый импульс на входе C сдвигает информацию влево, записывая состояние информационного входа D в освобождающийся левый триггер.

Задача таих регистров – преобразование данных из последовательного кода и наоборот.

Регистры в интегральном исполнении обычно более сложные и более многофункциональные. Их ассортимент очень велик.

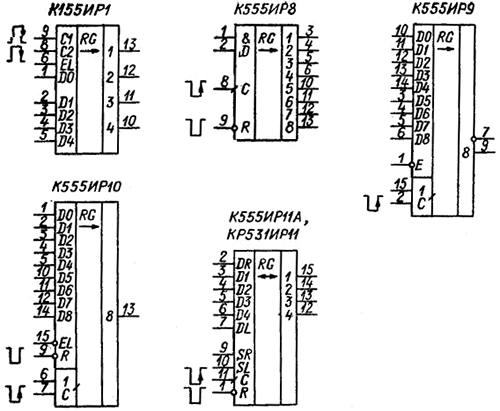

См., например, рис. 4.

Рис. 4.

Так, регистр ИР1 может загружать данные последовательно и параллельно (по двум независимым тактовым сигналам), сдвигать её.

ИР11 может сдвигать в любую сторону, имеет параллельную загрузку , вход сброса и т.д. Такие регистры могут использоваться для преобразования информации из последовательного кода в параллельный и наоборот.

Более подробно – см., например, [1].

Подобные многофункциональные устройства, кроме самих триггеров, содержат в себе ещё и некоторую логику (КС), которая управляет массивом этих триггеров, реализуя всё многообразие функций и режимов регистра.

1.2 Счётчики

Счётчик, в простейшем случае, это просто n счётных T-триггеров, соединённых последовательно – рис. 5.

Рис. 5. Простейший

двоичный счётчик

При подаче на вход тактовых импульсов, на выходах счётчика будут появляться коды 000, 001, 010, … 111, 000 (при n=3). Т.е. такая конструкция будет показывать, сколько импульсов пришло на её вход. По достижении счётчиком максимального значения (в нашем примере 111) при приходе на вход следующего импульса счётчик обнулится и продолжит счёт с нуля (000).

Реальные счётчики интегрального исполнения гораздо сложнее. Они имеют вход сброса, с помощью которого можно обнулить счётчик в любой момент времени, возможность загрузки в счётчик любого числа (т.е. он начинает счёт не с нуля, а с загруженного значения), возможность счёта в любом направлении (инкремент/декремент) и т.д.

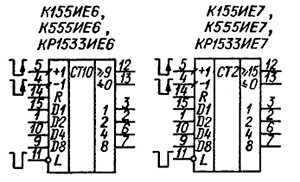

Рис. 6

Например, счётчики на рис. 6 могут считать вперёд и назад (входы +1/-1), имеют вход сброса R, параллельную предзагрузку значения (входы данных D1-D8 и вход строба L).

4-разрядные счётчики можно разделить на 2 группы – двоичные и двоично-десятичные. Первые пробегают все 16 значений 0000 .. 1111, вторые считают только до десяти (1010). Так, на рис. 23 счётчик ИЕ6 двоично-десятичный, а ИЕ7 - двоичный

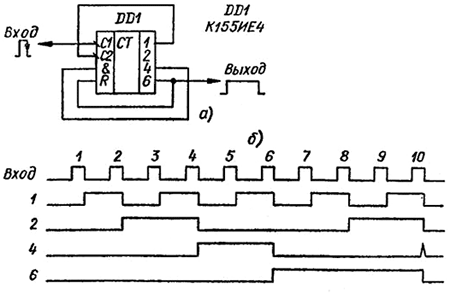

Из любого двоичного счётчика можно достаточно легко сделать двоично-десятичный – рис. 7.

Рис. 7

Двоично-десятичный счётчик из двоичного ИЕ4 и временная диаграмма его работы

Как можно заметить, микросхема ИЕ4, применяемая в данной схеме имеет два входа сброса, объединённые по И, что и позволяет собрать такую схему.

Обратное действие (двоичный счётчик из двоично-десятичного) нереализуемо.

Из временных диаграмм работы счётчиков (например, рис. 7) можно заметить, что частота импульсов на каждом следующем выходе счётчика в 2 раза меньше частоты на предыдущем выходе. Это означает, что любые счётчики могут быть использованы как делители частоты. Для получения коэффициентов деления, отличных от степеней двойки, можно применять, например, элемент И. По сути, счётчик на рис. 7 его и использует. Сигнал на выходе этого элемента появляется на каждом 10-м импульсе входной частоты fт.

Т.о., если взять любой двоичный счётчик (например, тот же ИЕ7), завести выходы 2 и 4 на элемент И, то на его выходе появятся импульсы с частотой fт/10.

Для получения регистров и счётчиков большой разрядности используют несколько микросхем. Некоторые счётчики (например, двоично-десятичный ИЕ9) имеют даже специальный выход переноса, который можно подать на вход следующего счётчика.

Раздел 2. Прочие логические схемы, выпускаемые промышленно

2.1 Дешифратор, шифратор

Дешифратор – КС, превращающая обычный двоичный код в одноединичный позиционный. В общем случае, для n входных (информационных) сигналов xi дешифратор имеет 2n выходных yi. При этом у него всегда активен только один выход.

ТИ дешифратора 2x4 имеет вид:

x1 |

x2 |

y1 |

y2 |

y3 |

y4 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

Промышленно выпускаемые ИМС дешифраторов (отечественные обозначаются буквами ИД в названии) обычно имеют инверсные выходы (т.е. неактивный вход == 1, активный == 0) и вход строба E (Enable), который позволяет "выключить" дешифратор - перевести все выходы в неактивное состояние вне зависимости от состояния xi. Также встречаются некие «урезанные» дешифраторы – 4 входа и 10 выходов для входных комбинаций 0000..1010. При остальных 6 комбинациях все выходы неактивны.

Кроме того, есть дешифраторы специального назначения, например, дешифрирующие 4-битный входной код в код для 7-сегментного индикатора и пр.

Синтез дешифраторов выполняется по общему принципу. Сигнал E можно учитывать при синтезе наряду с информационными, но проще поставить на каждый готовый выход yk элемент 2И (или 2И-НЕ), на один из входов которого подавать yk , а на второй сигнал E.

Шифратор – схема, обратная дешифратору. Т.е. она даёт на выходе код входа, на котором присутствует активный уровень. Входы шифраторов обладают приоритетами, т.е., если активный уровень подан сразу на несколько входов, то выходной код будет соответствовать входу с более высоким приоритетом. Пример шифратора – микросхема К155ИВ1.

2.2 Мультиплексоры, демультиплексоры

Мультиплексор – КС, коммутирующая состояние одного из информационных входов xi на единственный выход y. Поэтому их иногда называют коммутаторами.

Коммутируемый вход задаётся кодом на специальных адресных входах Ak. Обычно также есть вход разрешения работы E, при неактивном уровне на котором на выходе мультиплексора устанавливается неактивный уровень, а состояния информационных и адресных входов игнорируются.

Синтезировать можно как обычно, но, если учесть тот факт, что на адресные входы можно поставить готовый дешифратор нужной разрядности со своим входом Е, то вся остальная схема «вырождается» в набор 2И и элемент ИЛИ на выходе.

Микросхемы мультиплексоров имеют буквы КП в названии.

Демультиплексоры – схемы, обратные мультиплексорам. Они передают состояние единственного входа на указанный выход.

Многие зарубежные микросхемы мультиплексоров (например, 4051, 4052) могут выполнять и функции демультиплексора.

Для получения дешифраторов и мультиплексоров большой разрядности их можно включать каскадно, в некоторых случаях требуются дополнительные логические элементы.

2.3 Сумматоры и вычитатели

Сумматоры выполняют арифметическое сложение чисел (кодов). Их синтез был рассмотрен выше, но промышленностью выпускаются уже готовые полусумматоры и сумматоры, которые заметно упрощают построение различных схем.

В обычных схемах сумматоры применяются достаточно редко, основная сфера их применения – цифровые вычислительные системы. Подробно это будет рассмотрено в 3-й части.

Вычитатель реализует обратное действие – арифметическое вычитание чисел. Их можно синтезировать также как и сумматоры, но на практике сумматор и вычитатель это практически одно и то же. Более подробно это рассмотрено в части 3.

2.4 Схемы сравнения цифровых кодов

На их входы подаются 2 цифровых кода и они проводят их сравнение. Такие схемы обычно имеют 3 выхода – больше, меньше, равно – результат сравнения. Могут быть синтезированы как обычно. Как и сумматоры, используются в основном, в вычислительной технике.

Если требуется просто анализ «совпал-не совпал», то можно обойтись набором элементов XOR/XOR-NOT и элементом И/ИЛИ/И-НЕ/ИЛИ-НЕ. Такая схема гораздо проще и дешевле полноценной схемы сравнения.

2.5 Генераторы

Генератор – немаловажная и неотъемлемая часть многих устройств, особенно на базе микропроцессоров. Можно сказать, что это «сердце» таких конструкций.

Он представляет собой логическую схему, на выходе которой присутствуют импульсы некоторой частоты. В простейшем случае, генератором может быть один-единственный инвертор (или любое нечётное их количество), выход которого соединён с его же входом – рис. 8.

Рис. 8. Простейший генератор

на инверторе и временная диаграмма его работы

Но, несмотря на предельную простоту этой схемы, она не имеет никакого практического смысла, и работоспособна лишь теоретически, т.к. частота и прочие параметры импульсов такого генератора зависят (и очень сильно зависят) только от характеристик самого инвертора (быстродействие, пороги переключения и т.д.). Длительностью можно управлять лишь увеличивая/уменьшая кол-во инверторов в цепочке.

В реальности же на выходе могут получиться даже не импульсы, а какой-то непонятный, трудноповторяемый и труднопредсказуемый сигнал почти случайной формы, лишь отдалённо напоминающую прямоугольные импульсы. Кроме того, существует ещё и немалая зависимость от партии применяемых микросхем инверторов.

Поэтому, реальные генераторы это даже не цифровые на 100% схемы, а некие аналого-цифровые гибриды, содержащие в себе кроме логических элементов, ещё и чисто аналоговые детали – резисторы, конденсаторы, транзисторы и диоды.

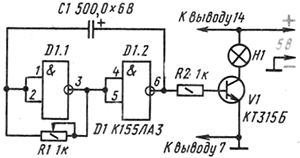

Рис. 9. Генератор на

микросхеме К155ЛА3

На рис. 9 (это скан из книги В. Борисова «Юный радиолюбитель») изображена схема генератора на 2-х инверторах. Резистором R1 можно менять частоту импульсов.

Работа такого генератора основана на периодическом заряде-разряде конденсатора C1 через входы-выходы инверторов.

Но схемы такого типа годятся только для детских игрушек и новогодних ёлочных гирлянд, т.к. частота у них полностью зависит от резистора и конденсатора. Даже если при настройке её точно настроить (с помощью R1), то течением времени конденсатор начнёт «подсыхать», его ёмкость будет меняться, вслед зачем изменится и частота, что не лучшим образом скажется на работе даже простых часов, не говоря уж о какой-нибудь сложной конструкции на микропроцессоре.

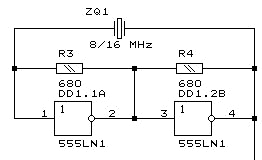

В микропроцессорной технике используются генераторы на основе кварцевого (или керамического) резонатора – рис. 10.

Рис 10. Генератор

прямоугольных импульсов на основе кварцевого резонатора

Преимущества таких схем заключается в том, что частота генерации зависит только от параметров резонатора и почти зависит от резисторов и прочих деталей, поэтому их номиналы можно слегка менять, а также не обращать внимания на обычный технологический разброс их параметров.

В ряде случаев могут понадобиться специальные генераторы с управляемыми параметрами импульсов (частота, скважность и т.д.). Для их построения служат микросхемы с буквами АГ, ГГ в названии [1]. Есть даже зарубежные микросхемы, совмещающие в себе генератор и двоичный счётчик (например, 4060).

Специализированные микросхемы генераторов позволяют управлять всеми параметрами генерируемых импульсов.

2.6 Повторители

Это схемы, реализующие функцию y=x. Ещё их называют усилителями-формирователями сигнала. Несмотря на их кажущуюся бессмысленность, они широко применяются в микропроцессорной (МП) технике.

Подробно это будет рассмотрено в 4-й части, но, забегая вперёд, отметим, что почти все МП системы имеют шинную архитектуру. Шина – это просто набор проводов, имеющих родственное функциональное назначение. Например, 4-х разрядный сумматор имеет 4 входа одного слагаемого, 4 входа другого, и 4 выхода. Каждую группу из этих 4 проводников можно назвать шиной. Это понятие позволяет более кратко описывать устройство вычислительных систем.

В МП системах есть много различных устройств, подключенных к одним и тем же шинам. Например, если нам необходимо реализовать и сложение и вычитание, то мы можем поставить 2 блока (микросхемы), реализующих эти действия – рис 11.

Рис. 11. Блок

суммирования-вычитания

Можно заметить, что входы обоих блоков одни и те же, т.е. они подключены к одним и тем же источникам сигнала. В реальных системах этих блоков гораздо больше – сумматоры, вычитатели, сдвигатели, умножители и т.д. и т.п.

Значит, источник должен быть достаточной мощности, чтобы быть в состоянии обслужить все эти блоки. Но часто источники не имеют таких возможностей, да и подключаемые к шинам устройства бывают очень разные по своим входными электрическим параметрам. Те же ТТЛ микросхемы бывают разные.

Например, 155 серия микросхем (вне зависимости от функционала конкретных микросхем) потребляет по входу раза в 3-4 больший ток (в среднем), чем 555 серия и т.д. Понятно, что в таких условиях нагрузочная способность один выход какого-либо источника на серию 555 в то же число раз выше, чем на 155 серию и т.д.

Чтобы иметь возможность подключать к шинам одновременно много устройств и реже задумываться о нагрузочной способности шины используют повторители сигнала. Повторяя уровни напряжения сигнала, они во много раз увеличивают максимально допустимый ток. Например, повторитель КР531АП2 обеспечивает выходной ток до 60 мА. Для сравнения у 155 серии этот ток составляет 16 мА, у 555 – 8 мА.

Существует ещё одна особенность МП шин. На рис. 11 каждый функциональный блок имеет свою выходную шину, независимую от выходной шины другого блока. Если мы просто соединим эти шины вместе, чтобы иметь одну общую шину, то получится ерунда – блоки будут мешать друг другу, выходная информация неизбежно исказится, а в худшем случае, выходные каскады блоков могут просто выйти из строя (сгореть). Чтобы этого не происходило, можно пойти 2-мя путями – поставить на выходе мультиплексор либо использовать блоки с третьим состоянием выхода. Мультиплексоры часто применяются в составе МП систем, а для подключения к шинам различных периферийных устройств используют повторители с Z состоянием. Когда выход повторителя находится в таком состоянии, то он отключен от остальной схемы, и практически «висит в воздухе», не мешая другим устройствам передавать что-то по тому же самому проводу, к которому он подключён.

Такие повторители выпускаются в виде готовых микросхем (например, К555АП6), многие из них являются двунаправленными, т.е. могут передавать данные в обе стороны, что соответствует идеологии МП систем, где, например, шина данных (ШД) используется и для чтения и для записи информации.

Все специализированные микросхемы (периферия, ПЗУ, ОЗУ и пр.), предназначенные для работы в составе МП систем уже имеют такие повторители в своём составе. Это позволяет очень просто подключать такие микросхемы к шине, не опасаясь того, что они помешают чему-то работать.

2.7. Запоминающие устройства

Запоминающее устройство – ЗУ. Предназначено для хранения цифровой информации, в основном в различных вычислительных системах.

ЗУ состоит из управляющих схем (это обычные КС, иногда в сочетании с простыми параллельными регистрами) и собственно набор (массив) ячеек памяти, запоминающих информацию.

ЗУ, как отдельный функциональный блок, имеет входы и выходы данных (шина данных ШД), адресные входы (шина адреса ША) и входы управления (шина управления ШУ) и характеризуется параметрами «ёмкость», «разрядность», «адресность» и «организация».

Ёмкость (информационная ёмкость) показывает, какой объём информации способно хранить запоминающее устройство. В общем случае она выражается в битах. Если ЗУ большой ёмкости, то её выражают в килобитах (кбит) или мегабитах (мбит). Делается это просто для удобства, т.к. очень часто проще манипулировать понятиями типа 4 кбит, а не 4096 бит и т.п.

Следует обратить внимание, что ёмкость ЗУ – величина, всегда кратная степени двойки, поэтому приставки кило- и мега- - это не привычные всем множители x1000 или x1000000. В цифровых устройствах приставка кило обозначает 210=1024, а мега - 220бит.

Организация говорит, как именно организовано то или иное ЗУ. Под этим понятием подразумевают структуру массива ячеек памяти. Например, выражение «организация 4096х1» или просто 4096x1 означает, что массив памяти организован как 4096 однобитовых запоминающих ячеек. Аналогично, 2048x8 – 2048 8-битовых ячеек. И т.д.

Разрядность – кол-во разрядов в одной ячейке. Кол-во входов/выходов ЗУ всегда равно этой величине.

Адресность – кол-во разрядов адреса. Оно равно двоичному логарифму кол-ва ячеек массива памяти.

Например, ЗУ с организацией 2048x4 будет иметь 11 адресных входов (log2(2048)=11, 211=2048) и 4 разрядные ШД.

Промышленно выпускаемые ЗУ имеют различную организацию. Например, отечественная микросхема ОЗУ КР537РУ10 имеет организацию 2Kx8 – 2048 8-битовых ячеек. Соответственно у неё 11 адресных входов и 8-битная ШД.

Для увеличения разрядности ЗУ ставят несколько микросхем «стандартной» разрядности, объединяя их ША и ШУ – рис 12.

Рис. 12. ЗУ разрядности

8 бит из 4-битных модулей (микросхем)

Как именно распределять разряды ШД по отдельным модулям ЗУ – непринципиально, главное, чтобы все сигналы ШД попадали на разные модули.

Если надо увеличить объём ЗУ, то на старшие разряды ША ставят дополнительный дешифратор адреса, а всё остальное объединяют – рис. 13.

Рис. 13. ЗУ большой

адресности из модулей с малой адресностью

Здесь мы видим дополнительный адресный дешифратор, который включает (активирует) один из 4 модулей памяти, в зависимости от 2-х старших бит адреса. Только выбранный модуль будет реагировать на все остальные сигналы. Дополнительный дешифратор обычно ставят на старшие биты адреса, хотя в некоторых случаях (например, для увеличения быстродействия) его можно ставить и на младшие.

Если необходимо увеличить и адресность и разрядность, используют одновременно оба способа. Принципы увеличения разрядности и адресности универсальны и применяются как для ОЗУ, так и для ПЗУ.

Подобные составные конструкции часто называют банками памяти. В них могут входить как ПЗУ, так и ОЗУ (см. ниже).

Реальные микросхемы ЗУ имеют вход CS (Chip Select), который разрешает им работать. Этот вход обычно инверсный, т.е. CS, что облегчает стыковку с подавляющим большинством дешифраторов, которые имеют инверсные выходы. Т.е., когда CS=1, микросхема полностью пассивна, она не реагирует на все остальные сигналы, а её выход находится в Z состоянии. Когда CS=0, она активна – работает.

Также следует отметить, что подавляющее большинство выпускаемых микросхем ЗУ единовременно могут выполнять только одну операцию (либо чтение, либо запись). Поэтому ШД у них одна, двунаправленная и всегда имеет тристабильные выводы, что позволяет без доп. ухищрений подключать их к ШД устройства.

Существует, так называемая двухпортовая память, которая может одновременно выполнять и чтение и запись по разным адресам, но это уже «товар специального назначения» и применяются она в основном в видеокартах компьютеров и прочих местах, где требуется строго одновременная работа с нею двух совершенно независимых и асинхронных по отношению друг к другу устройств. Здесь мы не будем её рассматривать.

ЗУ делятся на 2 класса – ОЗУ и ПЗУ.

4.7.1 ОЗУ

ОЗУ – оперативное запоминающее устройство, или RAM (англ. Random Access Memory). Важной особенностью ОЗУ является то, что оно хранит записанную в него информацию только тогда, когда на него подано питание. При обесточивании вся информация теряется. ОЗУ может и считывать и сохранять (записывать) информацию.

ОЗУ бывают 2-х типов – статические и динамические.

Статическое ОЗУ, СОЗУ (англ. SRAM – Static RAM) – по сути, набором триггеров плюс КС для управления ими (дешифрация адреса, схемы выборки и пр).

Как можно заметить, простейшее SRAM – регистр.

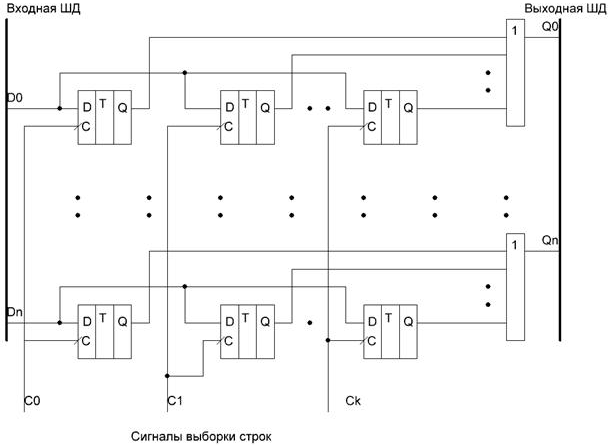

Внутреннюю структуру массива памяти RAM можно представить в виде набора синхронных D-триггеров, объединённых в матрицу – рис. 14.

Рис. 14. Обобщённая структура

массива памяти RAM

Сигналы выборки строк Cx вырабатываются адресным дешифратором микросхемы. Т.к. дешифратор в каждый момент времени активирует только одну строку, то выходные элементы ИЛИ не искажают (не перемешивают данные разных строк) информацию.

Микросхемы ОЗУ имеют также управляющие входы выборки (активации) CS, чтения RD и записи WR данных. Когда микросхема не выбрана, она не реагирует на управляющие сигналы, не воспринимает информацию ША, а её ШД находится в Z состоянии. Т.е. она полностью пассивна, находится в режиме хранения информации.

Динамическое RAM строится не на основе триггеров, а на основе конденсаторов. Преимущество такой памяти – заметно меньшие физические размеры ячейки памяти (можно создавать микросхемы огромной ёмкости) и удешевить всю конструкцию по сравнению с триггерными схемами. Основной недостаток – конденсаторы, хранящие информацию, вследствие различных токов утечки управляющих схем постепенно разряжаются и теряют записанную в них информацию. Для преодоления этого используют специальные схемы регенерации, задачей которых является поддержание заряда конденсаторов.

Несмотря на кажущуюся сложность подобных конструкций, такие ОЗУ очень часто применяются. Например, любые модули памяти для компьютеров (те самые SIMM и DIMM) – это память динамического типа.

Статическая память не содержит хранящих информацию конденсаторов и, поэтому, в регенерации не нуждается.

4.7.2 ПЗУ

Любые ПЗУ (постоянные или энергонезависимые запоминающие устройства, ROM) способны хранить информацию в выключенном состоянии. Запоминающие матрицы ROM создаются не на основе триггеров или конденсаторов, а на основе специальных материалов. «Обвязка» этой матрицы (адресные дешифраторы, буферы и пр.) в принципе мало чем отличается от своих RAM-аналогов. Часто встречающееся отличие – отсутствие в микросхемах ROM сигнала записи WR. Он заменяется специальными процедурами записи, реализуемыми различными программаторами – устройствами для записи данных в ROM.

Многие современные микросхемы ROM имеют простые интерфейсы программирования.

Существует много разных типов ROM (EPROM, EEPROM, flash и т.д.). Здесь мы не будем их рассматривать.

ROM применяются для хранения программ процессоров, различной служебной (например, конфигурационной) информации. Иногда на них строят специальные дешифраторы, логика работы которых отличается от всех стандартных вариантов.

Выборка данных из ПЗУ обычно происходит медленнее, чем из ОЗУ. Это связано с внутренними технологическими особенностями запоминающей матрицы.

Поэтому, в тех случаях, где требуется высокое быстродействие, используют т.н. «теневое копирование» – содержимое ПЗУ копируется в RAM такой же конфигурации (адресность и разрядность), ПЗУ «выключается», запись в подменяющий RAM блокируется и в дальнейшем информация только считывается из быстрого RAM, которое часто называют «теневым ПЗУ».

Этот приём иногда используется в материнских платах компьютеров, где очень быстрый центральный процессор вынужден проводить достаточно много времени, ожидая поступления данных из ПЗУ BIOS.

Литература, ссылки

1. Бирюков С.А. Применение ИМС

серий ТТЛ. Москва, изд. «Патриот» совместно с ред.

журнала «Радио», 1992 г.

2. Генераторы импульсов - http://www.radioman.ru/shem/other/1/impuls_generators.php

Автор: Павел Негробов (hd44780)

Негробов Павел

Негробов Павел

Опубликована: 2012 г.

Опубликована: 2012 г.

Вознаградить

Вознаградить

Комментарии (0) |

Я собрал (0) |

Подписаться

|

Я собрал (0) |

Подписаться

Для добавления Вашей сборки необходима регистрация