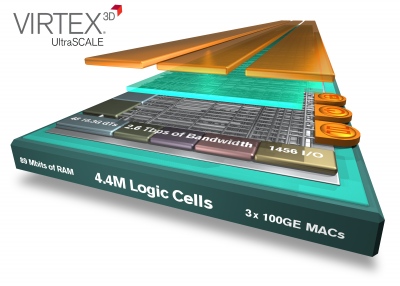

Компания Xilinx, Inc. заявила о новой интегральной схеме с рекордным количеством логических ячеек – до 4.4 миллиона, что в два раза больше по сравнению с самой высокой емкостью интегральной схемы Virtex®-7 2000T. Также как и высоко функциональная линейка программируемой логики UltraScale™ компании Xilinx, представленная сегодня, ИС Virtex® UltraScale™ VU440 3D увеличивает емкость с 2x при 28 нм техпроцессе до 4x при 20 нм техпроцессе, обеспечивая большую емкость по сравнению с другими программируемыми микросхемами. Используя улучшенную технологию 3D, ИС VU440 предоставляет больше уже при 20 нм техпроцессе, чем запланировано конкурирующими компаниями для 14/16 нм техпроцесса.

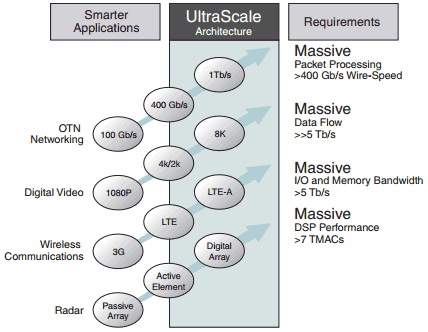

Интегральная схема Virtex UltraScale VU440 устанавливает новый промышленный ориентир, обеспечивая 50M эквивалентных специализированных ИС (ASIC) интеллектуальных драйверов для следующего поколения производства и создания прототипов. Микросхемы Virtex UltraScale по 20 нм техпроцессу также обеспечивают наивысшую производительность и пропускную способность системы для однокристальных исполнений 400G MuxSAR, 400G транспордеров и мостовых устройств 400G MAC Interlaken.

Семейство Virtex UltraScale предоставляет пользователям новый уровень производительности, интеграцию систем, а также полосу пропускания с дополнительными возможностями перепрограммирования. Масштабируемость ИС Virtex UltraScale VU440 обеспечивается благодаря архитектуре класса ASIC – эффективность использования до 90%, с маршрутизацией следующего поколения, ASIC-подобной синхронизацией, управлением электропитания, устранением узких мест коммутации и оптимизацией критических путей. Наряду с улучшениями основных архитектурных блоков, такими как расширение умножителей, каскадирование быстродействующей памяти, использование трансиверов с пиковой скоростью до 33 Гб/с, и добавление ведущей в отрасли интегрированной сетевой карты 100Гб/с Ethernet MAC и 150Гб/с Interlaken IP ядер, данные интегральные схемы обеспечивают производительность системы на уровне сотен гигабит в секунду с интеллектуальной обработкой при максимальной пропускной способности.

ИС Xilinx UltraScale используют преимущества ASIC-класса с единственной в отрасли программируемой архитектурой ASIC-класса, начиная от планарной технологии по 20 нм техпроцессу и заканчивая FinFET технологиями (транзисторы с вертикально расположенным затвором) по 16 нм техпроцессу, и от монолитных интегральных схем до 3D ИС. Посредством комбинации TSMC ведущей технологии и сопутствующей оптимизации с программным средством разработки Vivado ASIC-strength Design Suite, а также недавно представленной методики проектирования UltraFast™, компания Xilinx вырвалась на один-два года вперед, увеличив в 1.5 – 2 раза уровень производительности системы, улучшив также ее интеграцию.

Доступность

Интегральные микросхемы Xilinx® UltraScale™ поддерживаются программным средством разработки Vivado® Design Suite версии 2013.4. Полный пакет документации к продукту уже доступен по адресу www.xilinx.com/virtex-ultrascale. Для получения более подробной информации об архитектуре UltraScale посетите веб-сайт www.xilinx.com/ultrascale. Интегральные микросхемы Virtex UltraScale начнут поступать на рынок в первой половине 2014 года.

Опубликована: 18.12.2013

Опубликована: 18.12.2013

Вознаградить

Вознаградить

Комментарии (0) |

Я собрал (0) |

Подписаться

|

Я собрал (0) |

Подписаться

Для добавления Вашей сборки необходима регистрация